Marktgröße, Anteil und Branchenanalyse für Wafer-Level-Verpackungen, nach Typ (3D TSV WLP, 2,5D TSV WLP, Wafer Level Chip Scale Packaging (WLCSP), Nano WLP), nach Technologie (Fan-in Wafer Level Packaging (FI-WLP) und Fan-out Wafer Level Packaging (FO-WLP)), nach Endverwendung (Konsumelektronik, IT und Telekommunikation, Automobil, Gesundheitswesen und andere) und regionale Prognose, 2026–2034

WICHTIGE MARKTEINBLICKE

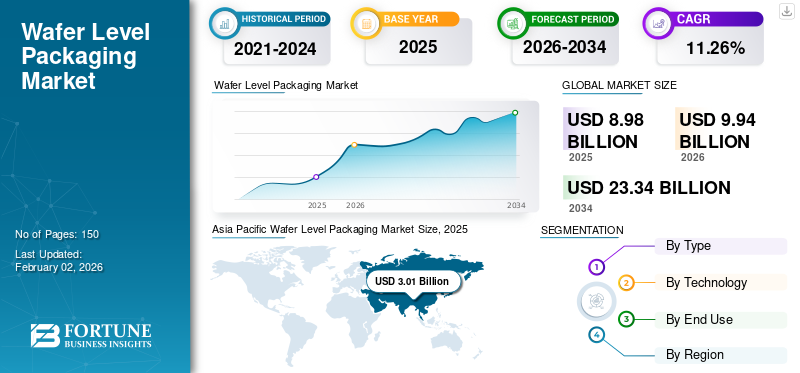

Die globale Marktgröße für Wafer-Level-Verpackungen wurde im Jahr 2025 auf 8,98 Milliarden US-Dollar geschätzt. Der Markt soll von 9,94 Milliarden US-Dollar im Jahr 2026 auf 23,34 Milliarden US-Dollar im Jahr 2034 wachsen und im Prognosezeitraum eine jährliche Wachstumsrate von 11,26 % aufweisen. Der asiatisch-pazifische Raum dominierte den Markt für Wafer-Level-Verpackungen mit einem Marktanteil von 33,53 % im Jahr 2025.

Wafer-Level-Packaging (WLP) ist eine Halbleiter-Packmethode, bei der integrierte Schaltkreise (ICs) direkt auf der Wafer-Stufe verpackt werden, bevor der Wafer in separate Chips zerteilt wird. Im Gegensatz zur herkömmlichen Verpackung, bei der die Chips vor dem Verpacken getrennt werden müssen, baut WLP Verbindungen, Schutzschichten und gelegentlich auch Umverteilungsschichten (RDLs) auf. Gleichzeitig bleiben die ICs Teil des Wafers. Diese Technik ermöglicht die Herstellung kleinerer, dünnerer und effizienterer Gehäuse und eignet sich daher ideal für leistungsstarke und kompakte elektronische Geräte.

Darüber hinaus umfasst der Markt mehrere wichtige Akteure, Amkor Technology, Taiwan Semiconductor Manufacturing Company Limited und Nordson Corporation, an der Spitze. Ein breites Portfolio mit innovativen Produkteinführungen und eine starke Ausweitung der geografischen Präsenz haben die Dominanz dieser Unternehmen auf dem Weltmarkt unterstützt.

Laden Sie ein kostenloses Muster herunter um mehr über diesen Bericht zu erfahren.

MARKTDYNAMIK

MARKTREIBER

Steigende Nachfrage nach miniaturisierter und leistungsstarker Elektronik treibt das Marktwachstum voran

Die zunehmende Tendenz zu kompakten, leichten und leistungsstarken elektronischen Geräten treibt den globalen Markt für Wafer-Level-Packaging erheblich an. B. Unterhaltungselektronik inklusiveSmartphonesAngesichts der Weiterentwicklung von Wearables und IoT-Geräten suchen Hersteller nach fortschrittlichen Verpackungslösungen, die eine höhere Funktionalität in kleinere Abmessungen integrieren können. Wafer-Level-Packaging bietet reduzierte Formfaktoren, eine verbesserte elektrische Leistung und einen überlegenen thermischen Wirkungsgrad und eignet sich daher für die Integration mit hoher Dichte. Darüber hinaus ermöglicht diese Technologie im Vergleich zu herkömmlichen Verpackungen niedrigere Produktionskosten und bessere Ausbeuteraten und fördert so ihre Verbreitung in der Unterhaltungs- und Automobilelektronikbranche weiter. Damit treibt es das weltweite Marktwachstum für Wafer-Level-Verpackungen voran.

MARKTBEGRENZUNGEN

Hohe Anfangsinvestitionen und komplexe Herstellungsprozesse behindern das Marktwachstum

Trotz seiner Vorteile stößt der Markt für Wafer-Level-Verpackungen auf Einschränkungen, die sich aus den erheblichen Kapitalinvestitionen und den technischen Feinheiten im Zusammenhang mit seinen Herstellungsprozessen ergeben. Die Einrichtung von WLP-Anlagen erfordert hochentwickelte Ausrüstung, präzise Wafer-Handhabungssysteme und strenge Reinraumbedingungen, was allesamt die Gesamtproduktionskosten in die Höhe treibt. Darüber hinaus erfordert die Integration von WLP in aktuelle Halbleiterfertigungslinien Spezialwissen und Prozessverfeinerung. Kleine und mittlere Halbleiterhersteller haben aufgrund begrenzter finanzieller und technischer Ressourcen häufig Schwierigkeiten, diese Technologien einzuführen, was möglicherweise eine breitere Umsetzung behindert.

MARKTCHANCEN

Die zunehmende Akzeptanz in Automobil- und 5G-Anwendungen schafft lukrative Wachstumschancen

Die zunehmende Integration von Elektronik in Fahrzeuge bietet zusammen mit der raschen Entwicklung der 5G-Infrastruktur erhebliche Wachstumsaussichten für Wafer-Level-Packaging-Technologien. Fortschrittliche Fahrerassistenzsysteme (ADAS),Elektrofahrzeuge (EVs),und vernetzte Fahrzeugtechnologien sind auf kompakte, hochzuverlässige Chips angewiesen – Bereiche, in denen WLP aufgrund seiner hervorragenden elektrischen Leistung und seines Wärmemanagements Spitzenleistungen erbringt. Ebenso erfordern 5G-Basisstationen und -Geräte Hochfrequenz-Chips mit geringer Latenz, was die Nachfrage nach WLP-Lösungen weiter erhöht. Die steigende Nachfrage von Rechenzentren, AR/VR-Geräten und KI-gesteuerten Edge-Computing-Systemen schafft auch neue Wachstumschancen für den Markt.

Markttrends für Wafer-Level-Verpackungen

Der Übergang zu Fan-Out und heterogener Integration zeichnet sich als Markttrend ab

Ein bedeutender Trend, der den globalen Wafer-Level-Packaging-Markt beeinflusst, ist der Übergang vom herkömmlichen Fan-In-WLP zu fortschrittlicherem Fan-Out-WLP und heterogenen Integrationstechnologien. Das Fan-out-Gehäuse ermöglicht eine höhere Ein-/Ausgabedichte (I/O) und bietet Platz für mehrere Dies in einem einzigen Gehäuse, wodurch es sich besonders für Hochleistungsrechnen, KI-Chips und mobile Prozessoren eignet. Darüber hinaus ist das Aufkommen von 3D-Stacking undSystem-in-Package (SiP)Architekturen verbessern die Funktionalität und minimieren gleichzeitig den Platzbedarf. Die zunehmende Zusammenarbeit zwischen Gießereien, OSATs (Outsourced Semiconductor Assembly and Test) und Materiallieferanten fördert Innovationen im WLP-Design und treibt den Markt in Richtung fortschrittlicherer, kostengünstigerer Lösungen.

HERAUSFORDERUNGEN DES MARKTES

Ertragsprobleme und Einschränkungen beim Wärmemanagement sind zentrale Herausforderungen für den Markt

Eine der größten Herausforderungen im Wafer-Level-Packaging-Bereich ist die Aufrechterhaltung hoher Ausbeuteraten während des gesamten Herstellungsprozesses, insbesondere bei fortschrittlichen Paketen, die große Wafer und Fine-Pitch-Verbindungen verwenden. Fehler, die beim Wafer-Handling oder beim Würfeln auftreten, können einen erheblichen Einfluss auf die Ausbeute und Rentabilität haben. Darüber hinaus wird die Steuerung der Wärmeableitung mit zunehmender Chipdichte immer komplexer. Während WLP im Vergleich zu herkömmlichen Verpackungsmethoden eine überlegene thermische Leistung bietet, stößt es immer noch auf Schwierigkeiten bei der Handhabung von Hochleistungsanwendungen ohne die Implementierung zusätzlicher Kühllösungen. Die Bewältigung dieser technischen Herausforderungen ist für die Verbesserung der Skalierbarkeit und die Gewährleistung der Zuverlässigkeit von Halbleiterbauelementen der nächsten Generation von entscheidender Bedeutung.

Laden Sie ein kostenloses Muster herunter um mehr über diesen Bericht zu erfahren.

Segmentierungsanalyse

Nach Typ

Hohe Leistungs- und Miniaturisierungsanforderungen für 3D TSV WLP steigerten das Segmentwachstum

Hinsichtlich der Art wird der Markt in 3D-TSV-WLP, 2,5D-TSV-WLP, Wafer-Level-Chip-Scale-Packaging (WLCSP) und Nano-WLP kategorisiert.

Es wird erwartet, dass das Segment des Typs 3D TSV WLP den Markt anführt und im Jahr 2026 weltweit 36,61 % beiträgt. Im Jahr 2025 wird das Segment voraussichtlich mit einem Anteil von 36,37 % dominieren. Das 3D Through-Silicon Via (TSV)-Wafer-Level-Packaging-Segment ist aufgrund seiner beispiellosen Fähigkeit, die steigenden Anforderungen an Leistung, Dichte und Energieeffizienz in Halbleiteranwendungen der nächsten Generation zu erfüllen, marktführend. TSV-basiertes WLP erleichtert das vertikale Stapeln mehrerer Chips oder Chips wie Logik, Speicher usw Sensoren, verbunden über mikroskopisch kleine Durchkontaktierungen, die direkt in das Silizium geätzt werden. Dieses Architekturdesign reduziert die Verbindungslängen erheblich, bietet Fortschritte in der Halbleitertechnologie und führt im Vergleich zu herkömmlichen 2D- oder Fan-Out-Konfigurationen zu größerer Bandbreite, geringerer Latenz, minimiertem Stromverbrauch und verbesserter Signalintegrität.

Das Segment Wafer Level Chip Scale Packaging (WLCSP) wird im Prognosezeitraum voraussichtlich mit einer durchschnittlichen jährlichen Wachstumsrate von 11,20 % wachsen.

Durch Technologie

Hohe I/O-Dichte und überlegene Leistungsmerkmale förderten das Wachstum des Segments

Technisch gliedert sich der Markt in Fan-in Wafer Level Packaging (FI-WLP) und

Fan-out-Wafer-Level-Packaging (FO-WLP).

Das Segment Fan-out Wafer Level Packaging (FO-WLP) wird voraussichtlich im Jahr 2026 einen dominanten Marktanteil von 57,94 % halten. Im Jahr 2025 wird das Segment voraussichtlich mit einem Anteil von 58,21 % dominieren. Das Segment Fan-Out Wafer Level Packaging (FO-WLP) führt den Markt für Wafer-Level-Packaging an, da es im Vergleich zu herkömmlichen Fan-In- und Wire-Bond-Packaging-Methoden eine höhere Eingangs-/Ausgangsdichte (I/O), eine verbesserte elektrische Leistung und eine außergewöhnliche Designflexibilität bietet. FO-WLP verbessert die Verbindungen über die Chip-Grundfläche hinaus, indem es den Chip in einen wiederhergestellten Wafer einbettet und so zusätzliche externe Verbindungen ermöglicht, ohne die Chipgröße zu vergrößern. Dieser Fortschritt ermöglicht die Entwicklung kompakter, leistungsstarker Geräte, die sich gut für moderne Anwendungen eignenUnterhaltungselektronik, mobile Prozessoren und Hochgeschwindigkeitskommunikationskomponenten.

Das Technologiesegment Fan-in Wafer Level Packaging (FI-WLP) wird im Prognosezeitraum voraussichtlich mit einer durchschnittlichen jährlichen Wachstumsrate von 11,89 % wachsen.

Nach Endverbrauch

Steigende Nachfrage nach kompakten und leistungsstarken Geräten treibt Segmentwachstum voran

Basierend auf der Endverwendung ist der Markt in Unterhaltungselektronik, IT und Telekommunikation, Automobil, Gesundheitswesen und andere unterteilt.

Erfahren Sie, wie unser Bericht Ihr Geschäft optimieren kann, Sprechen Sie mit einem Analysten

Im Jahr 2024 wurde der Weltmarkt hinsichtlich der Endverwendung von Unterhaltungselektronik dominiert. Darüber hinaus wird erwartet, dass das Segment im Jahr 2026 einen Anteil von 33,40 % ausmachen wird. Der Unterhaltungselektroniksektor ist führend auf dem Markt für Wafer-Level-Packaging (WLP), angetrieben durch die schnelle Expansion von Smartphones, Tablets, Wearables und verschiedenen tragbaren Geräten, die kompakte, leistungsstarke und energieeffiziente Chips erfordern. Die WLP-Technologie, die Fan-In-, Fan-Out- und 3D-TSV-Typen umfasst, erleichtert die Miniaturisierung vonIntegrierte Schaltkreise (ICs)Gleichzeitig gewährleisten sie eine hervorragende elektrische Leistung und ein hervorragendes Wärmemanagement – wesentliche Kriterien für moderne Verbrauchergeräte, die immer dünner und leistungsstärker werden.

Darüber hinaus ist die Massenproduktion von Unterhaltungselektronik ideal für die wirtschaftliche Wafer-Level-Verarbeitung von WLP geeignet, die die gleichzeitige Verpackung mehrerer Chips ermöglicht und so die Herstellungszeit und die Gesamtkosten senkt.

Darüber hinaus wird prognostiziert, dass der Automobil-Endverbrauch im Untersuchungszeitraum mit einer jährlichen Wachstumsrate von 11,37 % wachsen wird.

Regionaler Ausblick auf den Wafer-Level-Verpackungsmarkt

Geografisch ist der Markt in Europa, Nordamerika, den asiatisch-pazifischen Raum, Lateinamerika sowie den Nahen Osten und Afrika unterteilt.

ASIEN-PAZIFIK

Asia Pacific Wafer Level Packaging Market Size, 2025 (USD Billion)

Um weitere Informationen zur regionalen Analyse dieses Marktes zu erhalten, Laden Sie ein kostenloses Beispiel herunter

Auf den asiatisch-pazifischen Raum entfielen im Jahr 2025 3,01 Milliarden US-Dollar, was 33,53 % des weltweiten Marktanteils entspricht, und es wird erwartet, dass er im Jahr 2026 3,36 Milliarden US-Dollar erreichen wird. Der asiatisch-pazifische Raum ist führend auf dem globalen Markt für Wafer-Level-Verpackungen, wobei China, Japan und andere Länder an der Spitze stehen. Die robuste Halbleiterfertigungsinfrastruktur, die Präsenz wichtiger Gießereien wie TSMC, Samsung und UMC sowie bedeutende Produktionszentren für Unterhaltungselektronik sind ausschlaggebend für die Nachfrage nach WLP. Die zunehmende Verbreitung von 5G-Smartphones, Internet der Dinge (IoT)Geräte und Chips für künstliche Intelligenz (KI) haben diese Einführung weiter beschleunigt. Der japanische Markt soll bis 2026 ein Volumen von 0,64 Milliarden US-Dollar erreichen, der chinesische Markt soll bis 2026 ein Volumen von 1,1 Milliarden US-Dollar erreichen und der indische Markt soll bis 2026 ein Volumen von 0,91 Milliarden US-Dollar erreichen.

Schätzungen zufolge werden Indien und China im Jahr 2025 jeweils 0,81 und 0,98 Milliarden US-Dollar in der Region erreichen.

In anderen Regionen wie Nordamerika und Europa wird in den kommenden Jahren ein deutliches Wachstum erwartet.

NORDAMERIKA

Der nordamerikanische Markt erwirtschaftete im Jahr 2025 2,33 Milliarden US-Dollar, was 25,96 % der globalen Marktlandschaft entspricht, und wird im Jahr 2026 voraussichtlich 2,58 Milliarden US-Dollar erreichen. Nordamerika, insbesondere die USA, steht weiterhin an der Spitze des Halbleiterdesigns sowie der Forschung und Entwicklung und erleichtert die Implementierung von Wafer-Level-Packaging für Hochleistungsrechnen, KI-Beschleuniger und Rechenzentrumsanwendungen. Prominente Fabless-Unternehmen und robuste Partnerschaften zwischen Chipdesignern und OSATs (wie ASE, Amkor und TSMC North America Operations) treiben die Entwicklung von WLP weiterhin voran und kurbeln so das Marktwachstum in Nordamerika an. Der US-Markt soll bis 2026 ein Volumen von 2,08 Milliarden US-Dollar erreichen.

Im Jahr 2025 wird der US-Markt schätzungsweise 1,88 Milliarden US-Dollar erreichen.

EUROPA

Europa trug im Jahr 2025 mit einer Bewertung von 1,89 Milliarden US-Dollar 21,00 % zum Weltmarkt bei und wird im Jahr 2026 voraussichtlich 2,08 Milliarden US-Dollar erreichen. Die Automobil- und Industriesektoren prägen maßgeblich das Halbleiter-Ökosystem in Europa. Die Verbreitung von Wafer-Level-Packaging (WLP) nimmt rasant zu, angetrieben durch den wachsenden Bedarf an Sensoren, Leistungsgeräten und Radarsystemen in der Elektro- und Elektronikindustrieautonome Fahrzeuge. Darüber hinaus steht der Fokus der Region auf Energieeffizienz und Nachhaltigkeit im Einklang mit der Fähigkeit von WLP, den Stromverbrauch und die Materialverschwendung zu minimieren. Der britische Markt soll bis 2026 ein Volumen von 0,38 Milliarden US-Dollar erreichen, während der deutsche Markt bis 2026 ein Volumen von 0,45 Milliarden US-Dollar erreichen soll.

Unterstützt durch diese Faktoren wird erwartet, dass Länder wie das Vereinigte Königreich im Jahr 2025 einen Wert von 0,34 Milliarden US-Dollar, Deutschland einen Wert von 0,40 Milliarden US-Dollar und Frankreich einen Wert von 0,30 Milliarden US-Dollar verzeichnen werden.

Im Prognosezeitraum würden Lateinamerika sowie die Regionen Naher Osten und Afrika ein moderates Wachstum in diesem Markt verzeichnen.

LATEINAMERIKA

Lateinamerika trug im Jahr 2025 etwa 0,98 Milliarden US-Dollar zum Weltmarkt bei, was einem Anteil von 11,00 % entspricht, und wird im Jahr 2026 voraussichtlich 1,08 Milliarden US-Dollar erreichen. Der lateinamerikanische Markt wird im Jahr 2025 voraussichtlich eine Bewertung von 0,98 Milliarden US-Dollar verzeichnen. Der Markt für Wafer-Level-Packaging in Lateinamerika ist derzeit bescheiden, wächst jedoch, angetrieben durch eine steigende Nachfrage nach Unterhaltungselektronik, intelligenten Geräten und Automobilhalbleitern, insbesondere in Brasilien und Mexiko. Der Anstieg der Importe fortschrittlicher Chips für die lokale Montage und Elektronikfertigung fördert indirekt die Einführung von WLP, indem er die regionale Lieferkettenintegration verbessert.

MITTLERER OSTEN UND AFRIKA

Im Jahr 2025 hielten der Nahe Osten und Afrika 8,57 % des Weltmarktes und erreichten einen Wert von 0,77 Milliarden US-Dollar. Im Jahr 2026 wird ein Wachstum auf 0,84 Milliarden US-Dollar prognostiziert. Im Nahen Osten und Afrika wird Südafrika im Jahr 2025 voraussichtlich einen Wert von 0,22 Milliarden US-Dollar erreichen. Die Region befindet sich derzeit in der Anfangsphase des Marktes für Wafer-Level-Verpackungen; Es zeigt jedoch ein wachsendes Interesse, das durch die digitale Transformation verschiedener Branchen und die Expansion von vorangetrieben wirdintelligente StadtInitiativen und Verteidigungselektronikprojekte, insbesondere in der Golfregion.

WETTBEWERBSFÄHIGE LANDSCHAFT

Wichtige Akteure der Branche

Eine breite Palette an Produktangeboten, gepaart mit einem starken Vertriebsnetz wichtiger Unternehmen, unterstützten ihre führende Position

Die globale Wafer-Level-Packaging-Industrie weist eine halbkonzentrierte Struktur mit zahlreichen kleinen und mittleren Unternehmen auf, die weltweit aktiv sind. Diese Akteure sind aktiv an Produktinnovationen, strategischen Partnerschaften und der geografischen Expansion beteiligt.

Amkor Technology, Taiwan Semiconductor Manufacturing Company Limited und Nordson Corporation gehören zu den dominierenden Akteuren auf dem Markt. Ein umfassendes Sortiment an Einzeldosisverpackungsprodukten, globale Präsenz durch ein starkes Vertriebsnetz und Kooperationen mit Forschungs- und akademischen Instituten sind einige Merkmale dieser Akteure, die ihre Dominanz untermauern.

Darüber hinaus gehören zu den weiteren prominenten Marktteilnehmern Lam Research Corporation, MKS Inc., Jiangsu Changjiang Electronics Technology Co. Ltd. und andere. Diese Unternehmen ergreifen verschiedene strategische Initiativen, wie etwa Investitionen in Forschung und Entwicklung und Partnerschaften mit Pharmaunternehmen, um ihre Marktpräsenz zu stärken.

LISTE DER WICHTIGSTEN WAFER-LEVEL-VERPACKUNGSUNTERNEHMEN IM PROFIL

- Amkor-Technologie(UNS.)

- Taiwan Semiconductor Manufacturing Company Limited(Taiwan)

- Nordson Corporation(UNS.)

- Lam Research Corporation (USA)

- MKS Inc. (USA)

- Jiangsu Changjiang Electronics Technology Co. Ltd.(China)

- Fujitsu (Japan)

- MacDermid Alpha Electronics Solutions (USA)

- Mycronic (Schweden)

- Yield Engineering Systems (JA) (USA)

- ASE Global (Taiwan)

- ECI-Technologie (USA)

- Evatec AG (Schweiz)

- Nanotronik (USA)

- Kulicke und Soffa Industries, Inc. (Singapur)

WICHTIGE ENTWICKLUNGEN IN DER INDUSTRIE

- Oktober 2025:ASE Technology Holding Co., Ltd. und Analog Devices, Inc. gaben ihre strategische Zusammenarbeit in Penang, Malaysia, bekannt und unterzeichneten ein verbindliches Memorandum of Understanding. Bis zum Abschluss der endgültigen Transaktionsdokumente plant ASE den Erwerb von 100 % des Eigenkapitals von Analog Devices Sdn. Bhd., zusammen mit seiner Produktionsstätte in Penang.

- August 2025:Amkor Technology, Inc. gab aktualisierte Pläne für den Standort seines neuen Advanced bekanntHalbleiterVerpackungs- und Testanlage in Arizona. Die Anlage soll auf einem 104 Hektar großen Grundstück im Peoria Innovation Core im Norden von Peoria, Arizona, errichtet werden. Der Stadtrat von Peoria hat einstimmig einen Landtausch und eine überarbeitete Entwicklungsvereinbarung genehmigt, die Amkor den Handel mit seinem zuvor zugewiesenen 56 Hektar großen Grundstück innerhalb der Five North in der Gemeinde Vistancia ermöglichen.

- Oktober 2024:DELO stellte ein innovatives Verfahren für Fan-Out-Wafer-Level-Packaging (FOWLP) vor. Die Ergebnisse der Machbarkeitsstudie deuten darauf hin, dass durch die Verwendung von UV-härtbaren Formmaterialien anstelle von wärmehärtenden Alternativen eine deutliche Reduzierung von Verzug und Formverschiebung erzielt wird. Darüber hinaus verlängert dieser Ansatz die Aushärtezeit und reduziert den Energieverbrauch.

- September 2020:Die KLA Corporation stellte das Verpackungsinspektionssystem Kronos 1190 auf Waferebene, das Chip-Sortier- und Inspektionssystem ICOS F160XP sowie die neueste Version der ICOS T3/T7-Serie zur Inspektion und Messung verpackter integrierter Schaltkreiskomponenten (IC) vor. Diese neuen Werkzeuge zeichnen sich durch erhöhte Empfindlichkeit, verbesserten Durchsatz und hochmoderne Algorithmen aus, die darauf abzielen, die Herstellung von Halbleiterbauelementen während der Verpackungsphase zu verbessern und die Herausforderungen zu bewältigen, die sich aus immer kleiner werdenden Strukturgrößen, dreidimensionalen Strukturen und heterogener Integration ergeben.

- August 2019:Die Evatec AG gab bekannt, dass Evatec die neueste Generation ihres CLUSTERLINE-Dünnschichtabscheidungsgeräts geliefert hat, das über Verdampfungsfunktionen für SkyWater verfügt. Dieses Tool ermöglicht ein beispielloses Maß an Dünnschichtleistung, die für die Herstellung von Kohlenstoffnanoröhren und anderen neuen Technologien unerlässlich ist. Die CLUSTERLINE ist eine bewährte, hochvolumige Produktionslösung für die Einzelwaferverarbeitung, die die Integration der Prozesstechnologien PVD (Physical Vapour Deposition), hochionisiertes PVD, Soft Etch und PECVD (Plasma-Enhanced Chemical Vapour Deposition) ermöglicht.

BERICHTSBEREICH

Anfrage zur Anpassung um umfassende Marktkenntnisse zu erlangen.

Berichtsumfang und Segmentierung

| ATTRIBUT | DETAILS |

| Studienzeit | 2021-2034 |

| Basisjahr | 2025 |

| Geschätztes Jahr | 2026 |

| Prognosezeitraum | 2026-2034 |

| Historische Periode | 2021-2024 |

| Wachstumsrate | CAGR von 11,26 % von 2026 bis 2034 |

| Einheit | Wert (Milliarden USD) |

| Segmentierung |

Nach Typ · 3D TSV WLP · 2,5D TSV WLP · Wafer Level Chip Scale Packaging (WLCSP) · Nano-WLP Durch Technologie · Fan-in Wafer Level Packaging (FI-WLP) · Fan-out Wafer Level Packaging (FO-WLP) Nach Endverbrauch · Unterhaltungselektronik · IT und Telekommunikation · Automobil · Gesundheitspflege · Andere Nach Region · Nordamerika (nach Typ, Technologie, Endverwendung und Land) o USA o Kanada · Europa (nach Typ, Technologie, Endverwendung und Land/Subregion) o Deutschland o Großbritannien o Frankreich o Spanien o Italien o Russland o Polen o Rumänien o Restliches Europa · Asien-Pazifik (nach Typ, Technologie, Endverwendung und Land/Subregion) o China o Japan o Indien o Australien o Südostasien o Rest des asiatisch-pazifischen Raums · Lateinamerika (nach Typ, Technologie, Endverwendung und Land/Subregion) o Brasilien o Mexiko o Argentinien o Rest Lateinamerikas · Naher Osten und Afrika (nach Typ, Technologie, Endverwendung und Land/Subregion) o Saudi-Arabien o VAE o Oman o Südafrika o Rest des Nahen Ostens und Afrikas |

Häufig gestellte Fragen

Laut Fortune Business Insights lag der globale Marktwert im Jahr 2025 bei 8,98 Milliarden US-Dollar und soll bis 2034 23,34 Milliarden US-Dollar erreichen.

Im Jahr 2025 lag der Marktwert bei 3,01 Milliarden US-Dollar.

Es wird erwartet, dass der Markt im Prognosezeitraum 2026–2034 eine CAGR von 11,26 % aufweisen wird.

Das Segment Fan-out Wafer Level Packaging (FO-WLP) war technologisch führend auf dem Markt.

Die Schlüsselfaktoren für das Marktwachstum sind die steigende Nachfrage nach miniaturisierter und leistungsstarker Elektronik.

Amkor Technology, Taiwan Semiconductor Manufacturing Company Limited, Nordson Corporation, Lam Research Corporation, MKS Inc. und Jiangsu Changjiang Electronics Technology Co. Ltd. sind einige der führenden Akteure auf dem Markt.

Der asiatisch-pazifische Raum dominierte den Markt im Jahr 2025.

Die hohe Nachfrage nach Wafer-Level-Gehäusen aus dem Unterhaltungselektroniksektor ist einer der Faktoren, die die Produkteinführung voraussichtlich begünstigen werden.

Nehmen Sie Kontakt mit unseren Experten auf Sprechen Sie mit einem Experte

20% kostenlose Anpassung erhalten

Regionale und länderspezifische Abdeckung erweitern, Segmentanalyse, Unternehmensprofile, Wettbewerbs-Benchmarking, und Endnutzer-Einblicke.

-

US +1 833 909 2966 (Gebührenfrei)

-

Nehmen Sie Kontakt mit uns auf