Marktgröße, Anteil und Branchenanalyse für 3D-Stacking, nach Methode (Die-to-Die, Die-to-Wafer, Wafer-to-Wafer, Chip-to-Chip und Chip-to-Wafer), nach Technologie (3D TSV (Through Silicon Via), 3D Hybrid Bonding, monolithische 3D-Integration und andere), nach Gerät (MEMS/Sensoren, Bildgebung und Optoelektronik, Logik-ICs, Speichergeräte, LEDs und andere), Nach Branche (IT & Telekommunikation, Unterhaltungselektronik, Automobil, Fertigung, Gesundheitswesen und andere) und regionale Prognose, 2026 – 2034

WICHTIGE MARKTEINBLICKE

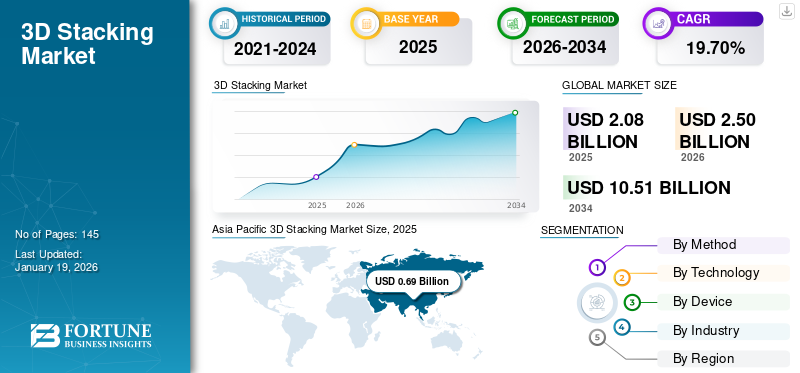

Die globale Marktgröße für 3D-Stacking wurde auf USD geschätzt2.08Milliarden im Jahr 2025. Der Markt wird voraussichtlich ab USD wachsen2,50Milliarden im Jahr 2026 auf USD10.51Milliarden bis 2034, was einem CAGR von entspricht19.70% im Prognosezeitraum.

3D-Stacking, auch bekannt als 3D-Integration oder 3D-IC-Stacking, ist eine fortschrittliche Halbleiter-Packaging-Technologie, bei der mehrere Schichten integrierter Schaltkreise (ICs) oder Chips vertikal zu einem einzigen kompakten Gehäuse gestapelt werden. Diese gestapelten Schichten werden über Through-Silicon Vias (TSVs), Mikro-Bumps oder Wafer-zu-Wafer-/Chip-zu-Wafer-Bonding miteinander verbunden, was eine schnellere Datenübertragung und eine verbesserte Leistung ermöglicht.

Die rasche Ausweitung von Halbleiteranwendungen in verschiedenen Branchen und die Integration fortschrittlicher Elektronik in den Automobilsektor deuten auf große Chancen für das Marktwachstum hin. Darüber hinaus subventioniert die zunehmende Einführung der 3D-Stack-Technologie zur Bereitstellung kürzerer Verbindungen und zur Reduzierung des Stromverbrauchs das Marktwachstum weiter. Diese Technologie ermöglicht eine schnellere Datenverarbeitung und verringert die Latenz, wodurch Datenanalyse, maschinelles Lernen usw. gefördert werdenCloud-Computing.

Verschiedene auf dem Markt tätige Unternehmen, darunter Taiwan Semiconductor Manufacturing Company Limited (TSMC), Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Cadence Design Systems, Inc., Texas Instruments Inc. und andere. Diese Akteure haben verschiedene Strategien übernommen, um ihre Marktpositionen zu stärken und die Marktdurchdringung in der 3D-Stacking-Branche zu erhöhen. Zum Beispiel,

- Im September 2024,Samsung kündigte seine Pläne zur Massenproduktion von 3D-Stack-System-on-Chip (SoC) im Jahr 2026 an. Ziel des Unternehmens ist es, die Leistung zu steigern und die Herausforderungen der Halbleiterminiaturisierung zu bewältigen, indem es Halbleiter mit unterschiedlichen Funktionalitäten stapelt.

DerHalbleiterindustriereagiert empfindlich auf Störungen der globalen Lieferkette, wie sie während der COVID-19-Pandemie zu beobachten waren. Die durch die Pandemie verursachte Nachfrage belastete die Kapazitäten an allen Stellen der Lieferkette, angefangen bei den Komponentenlieferanten. Die COVID-19-Pandemie hat die Chipknappheit ausgelöst, und ihre weitreichenden Auswirkungen, darunter Virusausbrüche, arbeitsrechtliche Herausforderungen und geopolitische Unsicherheiten, haben sie weiter verschärft. Dies hatte das Marktwachstum vorübergehend behindert; Es wird jedoch erwartet, dass die Branche in den kommenden Jahren das Niveau vor der Pandemie erreichen wird.

Laden Sie ein kostenloses Muster herunter um mehr über diesen Bericht zu erfahren.

AUSWIRKUNGEN GENERATIVER KI

Einführung generativer KI zur Beschleunigung des Design- und Simulationsprozesses zur Förderung der Marktexpansion

Generative KI beeinflusst maßgeblich die Marktexpansion, insbesondere im Halbleitersektor. Diese Auswirkungen sind in mehreren Bereichen sichtbar, darunter Designinnovation, Fertigungseffizienz und Marktdynamik.

Generative KI verbessert die Entwurfsphase des 3D-Stacks, indem sie die Erstellung verbesserter Layouts und Simulationen automatisiert. Tools wie generative Designalgorithmen ermöglichen es Ingenieuren, verschiedene Designmöglichkeiten zu erkunden, was zu effizienteren und innovativeren 3D-Stapelarchitekturen führt. Diese Beschleunigung der Designprozesse ist von entscheidender Bedeutung, da die Branche versucht, den steigenden Anforderungen von Anwendungen wie zKünstliche Intelligenz (KI)und Hochleistungsrechnen.

MARKTDYNAMIK

Markttrends für 3D-Stacking

Fortschritte in der Chip-Verpackungstechnologie sollen das Marktwachstum vorantreiben

Die vielfältigen Anwendungen von 3D-Stacking-Technologien treiben das Wachstum des 3D-Stacking-Marktes voran. Wichtige Plattformen wie 3D NAND, 3D SoC und CBA DRAM sowie Technologien wie 3D-Stacked-Memory spielen eine entscheidende Rolle bei der Erfüllung der Leistungs-, Miniaturisierungs- und Leistungsanforderungen moderner Elektronik. Chiplet-basierte Designs und heterogene Integration verändern die Halbleiterarchitektur. Große Branchenakteure wie Intel, TSMC, Nvidia und AMD investieren erheblich in diese Lösungen, indem sie Hybrid-Bonding nutzen, um die Verbindungsabstände zu verbessern.

In den kommenden Jahren werden Trends wie 3.5DVerpackungund Panel-Level-Packaging dürften den Markt erheblich beeinflussen, angetrieben durch die wachsende Nachfrage nach Hochleistungsrechnern und KI-Lösungen. Die Wettbewerbslandschaft verändert sich, da Gießereien und IDM-Unternehmen ihre Verpackungsfähigkeiten ausbauen, während neue Marktteilnehmer aus China den Wettbewerb verschärfen. Da die herkömmliche Chip-Miniaturisierung an ihre physikalischen Grenzen stößt, setzt die Branche zunehmend auf fortschrittliche Verpackungstechniken, um Leistung und Integration zu verbessern.

Markttreiber

Steigende Nachfrage nach KI und Rechenzentren treibt das Marktwachstum voran

Aufgrund der zunehmenden Bedeutung von Daten in der heutigen Welt ist die Nachfrage nach Rechenzentren bereits stark gestiegen. Es wird jedoch erwartet, dass diese Nachfrage mit dem Anstieg von weiter wächstgenerative KI (gen AI). Die 3D-Chip-Stacking-Technologie wirkt sich positiv auf die Rechenzentren aus und eröffnet neue Möglichkeiten zur Kostenoptimierung.

Die Infrastruktur von Rechenzentren weltweit entwickelt sich rasant weiter, um KI-Funktionen zu unterstützen und die Verarbeitung großer Mengen komplexer Berechnungen und Anforderungen zu ermöglichen. Die Regionen Asien-Pazifik und Nordamerika sind derzeit führend bei der Verbreitung von Rechenzentren, mit wichtigen Hubs in Städten wie Peking, Shanghai, Nord-Virginia und der San Francisco Bay Area. Laut einem Bericht des IBM Institute for Business Value (IBM IBV) aus dem Jahr 2024 haben 43 % der C-Level-Technologiemanager in den letzten sechs Monaten aufgrund des Aufstiegs generativer KI wachsende Bedenken hinsichtlich ihrer Technologieinfrastruktur geäußert, sodass sie sich auf die Optimierung ihrer Infrastruktur konzentrieren können, um deren Skalierungsanforderungen gerecht zu werden.

Bemerkenswerte Investitionen großer Technologieunternehmen deuten auch auf ein starkes Wachstum des KI-Rechenzentrumssektors hin. Im Jahr 2025 will Microsoft rund 80 Milliarden US-Dollar in den Bau von Rechenzentren investieren, während Meta 10 Milliarden US-Dollar in ein neues, vier Millionen Quadratmeter großes Hyperscale-Unternehmen investiertRechenzentrumProjekt in Louisiana.

Marktherausforderungen

Komplexität der Herstellung und erhöhte Kosten behindern die Weiterentwicklung des Marktes für 3D-Stacking

Eine der größten Herausforderungen bei der Implementierung des 3D-Chip-Stackings ist die erhöhte Fertigungskomplexität. Der Prozess erfordert fortschrittliche Fertigungstechniken und hochspezialisierte Ausrüstung, was die Produktionskosten erheblich erhöhen kann. Darüber hinaus kann diese Komplexität zu Ertragsproblemen führen, die sich weiter auf die Fertigungskompetenz und -effektivität auswirken.

Darüber hinaus tragen die für 3D-Stacks wesentlichen Materialien – wie Silizium-Interposer, Through-Silicon Vias (TSVs) und Fine-Pitch-Mikrobumps – zu erhöhten Produktionskosten bei. Diese Komponenten erfordern anspruchsvolle Fertigungsprozesse, was den Material- und Prozessaufwand in die Höhe treibt. Um die Kompatibilität mit bestehenden Hardwarearchitekturen, Softwareschnittstellen und Wärmemanagementsystemen zu gewährleisten, sind häufig erhebliche Investitionen und Änderungen auf Systemebene erforderlich. Infolgedessen können diese Herausforderungen die breitere Einführung von 3D-Stack-Technologien verlangsamen.

Laden Sie ein kostenloses Muster herunter um mehr über diesen Bericht zu erfahren.

Marktchancen

Aktive Regierungsinitiativen und Investitionen zur Erschließung neuer Wachstumswege

Regierungsprogramme, darunter das U.S. CHIPS und der Science Act, ermöglichen erhebliche Investitionen in die Halbleiterfertigung. Diese Initiativen zielen darauf ab, die inländischen Produktionskapazitäten zu verbessern und die Abhängigkeit von ausländischen Lieferketten zu verringern, wodurch Wachstumsmöglichkeiten geschaffen werdenfortschrittliche VerpackungTechnologien, einschließlich 3D-Stacking. Zum Beispiel,

- Im Juni 2025Micron Technology Inc. kündigte eine bahnbrechende Investition von rund 200 Milliarden US-Dollar in die Fertigung und Forschung und Entwicklung in den USA an und unterstreicht damit Amerikas Bemühungen, die Führungsrolle in der globalen Halbleiterindustrie zurückzugewinnen. Diese Expansion wird maßgeblich von der US-Regierung unterstützt, wobei Micron voraussichtlich rund 6,5 Milliarden US-Dollar an Unterstützung im Rahmen des CHIPS and Science Act erhalten wird.

Darüber hinaus unterstreichen bedeutende Investitionen von Branchenführern – wie die 2,9 Milliarden US-Dollar teure Chip-Packaging-Anlage von TSMC und die 110 Millionen US-Dollar teure Erweiterung der Chip-Polierkapazitäten von Fujifilm – Taiwans anhaltendes Engagement für die Weiterentwicklung der Halbleiter-Exzellenz.

SEGMENTIERUNGSANALYSE

Nach Methode

Die-to-Wafer-3D-Stacking für kundenspezifische Chiplösungen treibt das Segmentwachstum voran

Basierend auf der Methode wird der Markt in Die-to-Die, Die-to-Wafer, Wafer-to-Wafer, Chip-to-Chip und Chip-to-Wafer unterteilt.

Es wird erwartet, dass das Die-to-Wafer-Verfahren im Jahr 2026 mit 28,08 % den größten Marktanteil gewinnen wird, da es den Anforderungen an leistungsstarke, kostengünstige und zuverlässige Halbleiterverpackungen gerecht wird. Die D2W-Methode ermöglicht die Integration verschiedener Arten von Chips (z. B. Logik, Speicher,Sensoren) in einem einzigen Paket. Dies ist von Bedeutung für sich entwickelnde Anwendungen, die kundenspezifische Chiplösungen benötigen, wie etwa KI, 5G und IoT, wodurch der potenzielle Markt für 3D-Stack-Technologien wächst. Zum Beispiel,

- Im Mai 2025,SÜSS, ein globaler Anbieter von Halbleiterausrüstung und Prozesslösungen, hat die XBC300 Gen2 D2W-Plattform auf den Markt gebracht – eine fortschrittliche Bondlösung, die sein Hybrid-Bond-Portfolio verbessert. Diese neue Plattform unterstützt das Die-to-Wafer (D2W)-Bonden auf 200-mm- und 300-mm-Substraten, erfüllt strenge Anforderungen an den Abstand zwischen den Chips und ermöglicht eine hochpräzise Integration für Halbleiterbauelemente der nächsten Generation.

Es wird jedoch prognostiziert, dass die Wafer-zu-Wafer-Methode im Prognosezeitraum die höchste CAGR verzeichnen wird. Wafer-zu-Wafer-Verbindungen verzeichnen aufgrund ihrer Miniaturverbindungspunkte und hochertragreichen Fertigungsangebote ein schnelles Wachstum, was sie ideal für die Speicherintegration, neuromorphe Verarbeitungsanwendungen und Bildsensortechnologien macht.

Durch Technologie

Die zunehmende Einführung von 3D TSV für fortschrittliche Verpackungslösungen katalysiert das Segmentwachstum

Basierend auf der Technologie ist der Markt in 3D-TSV (Through Silicon Via), 3D-Hybrid-Bonding, monolithische 3D-Integration und andere unterteilt.

Im Jahr 2026 dürfte die 3D-TSV-Technologie (Through-Silicon Via) mit 33,92 % den größten Marktanteil halten. Hervorhebung seiner entscheidenden Rolle bei der Unterstützung der vertikalen Integration in Halbleiterbauelementen. TSVs fungieren als vertikale elektrische Verbindungen und erleichtern die Erstellung innovativer 3D-Pakete und integrierter Schaltkreise durch die direkte Verbindung gestapelter Halbleiterchips. Diese Taktik macht die herkömmliche Kantenverdrahtung oder Drahtbondung überflüssig, die früher bei gestapelten Paketen auf organischen Substraten verwendet wurde. Aufgrund ihrer überlegenen Leistung und kompakten Integrationsmöglichkeiten werden TSVs zunehmend bei der Herstellung modernster Technologien bevorzugt3D-ICsund Interposer-basierte Architekturen.

Es wird erwartet, dass das 3D-Hybrid-Bonding im Prognosezeitraum die höchste CAGR verzeichnen wird, was auf steigende Investitionen in fortschrittliche Chip-Stacking-Technologien zurückzuführen ist. Diese Bonding-Methode verbindet Metall-zu-Metall- und Dielektrikum-zu-Dielektrikum-Schnittstellen, wodurch der Verbindungswiderstand erheblich reduziert und die Signalintegrität verbessert wird. Dadurch bietet es eine überragende Energieeffizienz, Leistung und Skalierbarkeit – wichtige Anforderungen für KI-Beschleuniger, High-Performance-Computing-Prozessoren (HPC) und Hochgeschwindigkeitsspeicherlösungen.

Nach Gerät

Steigende Nachfrage nach High-Bandwidth Memory (HBM), um die Expansion des Speichergerätesegments anzukurbeln

Je nach Gerät ist der Markt in MEMS/Sensoren, Bildgebung und Optoelektronik, Logik-ICs, Speichergeräte, LEDs und andere unterteilt.

Es wird erwartet, dass Speichergeräte eine entscheidende Rolle bei der Entwicklung des 3D-Stacking-Marktes spielen und im Jahr 2026 einen Anteil von 27,37 % ausmachen werden. Angetrieben durch die steigende Nachfrage nach höherer Leistung, höherer Dichte und kompakten Formfaktoren. Der Anstieg datenintensiver Anwendungen – wie künstliche Intelligenz (KI), Cloud Computing und High Performance Computing (HPC) – hat die Einführung von 3D-Stacked-Speicherlösungen beschleunigt, darunter 3D NAND, High-Bandwidth Memory (HBM) und fortschrittliches DRAM. Als Reaktion auf den wachsenden Bedarf an schnellem Speicher mit geringer Latenz investieren führende Unternehmen wie Samsung, Micron und SK Hynix erheblich in 3D-NAND-Stacking und TSV-basierte HBM-Technologien, um die Speicherdichte zu erhöhen und gleichzeitig die Energieeffizienz zu steigern.

Es wird erwartet, dass die Logik-ICs zwischen 2025 und 2032 die höchste CAGR verzeichnen. Die wachsenden heterogenen Computer-Workloads,Maschinelles Lernen (ML)Komplexität und künstliche Intelligenz (KI) treiben die Nachfrage nach gestapelten 3D-Logik-ICs voran, insbesondere für FPGAs, KI-Beschleuniger und Prozessoren. Zum Beispiel,

- Im August 2024,Die Powerchip Semiconductor Manufacturing Company (PSMC) hat ihre 2,5D-Interposer mit Logic-DRAM-Mehrschicht-Wafer-Stacking-Technologie eingeführt, um den wachsenden Anforderungen von KI-Anwendungen gerecht zu werden. Nach Angaben des Unternehmens planen große Player – darunter AMD –, diese Technologie mit fortschrittlichen Logikknoten führender Hersteller zu nutzen, um 3D-KI-Chips mit hoher Kapazität, geringem Stromverbrauch und hoher Bandbreite zu entwickeln.

Nach Branche

Erfahren Sie, wie unser Bericht Ihr Geschäft optimieren kann, Sprechen Sie mit einem Analysten

Steigende 5G-Netzwerkinfrastruktur und Bedarf an Lösungen mit geringer Latenz, um die Einführung von 3D-Stacking in der IT und Telekommunikation voranzutreiben

Nach Branchen ist der Markt in IT &Telekommunikation, Unterhaltungselektronik, Automobil, Fertigung, Gesundheitswesen und andere.

Der IT- und Telekommunikationssektor wird im Prognosezeitraum voraussichtlich mit der höchsten CAGR wachsen, was auf das schnelle Wachstum des Datenverbrauchs, den Aufstieg von 5G und verwandter Technologien sowie den steigenden Bedarf an leistungsstarken, kompakten und energieeffizienten Halbleiterlösungen zurückzuführen ist. Die Einführung von 5G-Netzen ist einer der Haupttreiber für die zunehmende Einführung der 3D-Stack-Technologie im Telekommunikationssektor. Da 5G höhere Datengeschwindigkeiten, geringe Latenz und eine effizientere Kommunikation zwischen Netzwerkknoten erfordert, bieten 3D-Stacked-Halbleiter die notwendigen Leistungsverbesserungen.

- Im Juni 2025Soitec, ein Anbieter von Halbleitermaterialien, gab eine strategische Partnerschaft mit der Powerchip Semiconductor Manufacturing Company (PSMC) bekannt. Im Rahmen dieser Zusammenarbeit verpflichtet sich Soitec, PSMC mit 300-mm-Substraten zu beliefern, die über eine Trennschicht und die Fähigkeit zum Transistor Layer Transfer (TLT) verfügen. Dies wird das fortschrittliche 3D-Chip-Stacking auf Waferebene unterstützen und das Potenzial der Halbleitertechnologien der nächsten Generation verdeutlichen.

DerUnterhaltungselektronikindustriehielt im Jahr 2024 den größten Marktanteil, angetrieben durch die zunehmende Verbreitung von Hochleistungs-Tablets, Smart Wearables und Smartphones mit integrierter AR/VR-Funktion. Diese Geräte erfordern eine energieeffiziente Hochgeschwindigkeitsverarbeitung und kompakte 3D-Stapelspeicherlösungen für Verbraucher wie 3D NAND und HBM sowie fortschrittliche Logik-ICs, um die Batterielebensdauer und die Gesamtleistung des Geräts zu verlängern.

Regionaler Ausblick auf den 3D-Stacking-Markt

Geografisch wird der Markt in den asiatisch-pazifischen Raum, Nordamerika, Südamerika, Europa sowie den Nahen Osten und Afrika untersucht.

Asien-Pazifik

Asia Pacific 3D Stacking Market Size, 2025 (USD Billion)

Um weitere Informationen zur regionalen Analyse dieses Marktes zu erhalten, Laden Sie ein kostenloses Beispiel herunter

Asien-Pazifik dominierte den Markt mit einer Bewertung von 0,69 Milliarden US-Dollar im Jahr 2025 und wird voraussichtlich 0,82 Milliarden US-Dollar im Jahr 2026 erreichen. Der asiatisch-pazifische Raum hielt im Jahr 2024 den größten Anteil am 3D-Stacking-Markt, angetrieben durch die Wettbewerbsvorteile der Region. Dazu gehören die Verfügbarkeit kostengünstiger Arbeitskräfte in China, kontinuierliche Innovationen durch Fabriken in Taiwan, starke Fertigungskapazitäten japanischer Unternehmen und die Errichtung neuer Halbleiterfabriken in China, Taiwan, Japan und Südkorea. Der japanische Markt soll bis 2026 ein Volumen von 0,19 Milliarden US-Dollar erreichen, der chinesische Markt soll bis 2026 ein Volumen von 0,23 Milliarden US-Dollar erreichen und der indische Markt soll bis 2026 ein Volumen von 0,11 Milliarden US-Dollar erreichen.

Die staatliche Unterstützung beschleunigt das Wachstum des Marktes im asiatisch-pazifischen Raum weiter. Japans Investitionen in Höhe von 11,6 Milliarden US-Dollar in die Entwicklung der Halbleitertechnologie im Jahr 2023, von denen 30 % für fortschrittliche Verpackung und 3D-Stacking vorgesehen sind, kurbeln die Branchenexpansion erheblich an. Ebenso stärkt Südkoreas Zusage von 427 Milliarden US-Dollar an Halbleiterinvestitionen bis 2030 (Ministerium für Handel, Industrie und Energie) das Halbleiter-Ökosystem der Region.

Der chinesische Markt hatte im Jahr 2024 den größten Marktanteil im asiatisch-pazifischen Raum. Das Wachstum des Marktes wird in erster Linie durch die schnelle Ausweitung der inländischen Halbleiterfertigung angetrieben, die durch Regierungsinitiativen wie Chinas „Made in China 2025“-Plan unterstützt wird. Darüber hinaus befeuert die Führungsrolle des Landes bei KI- und IoT-Anwendungen, die stark auf heterogener Integration und Speicher mit hoher Bandbreite (HBM) basieren, die Nachfrage. Der Anstieg des Bedarfs an5G-Chipsätze, KI-Prozessoren und Elektronik für autonome Fahrzeuge beschleunigen die Einführung fortschrittlicher 3D-Integration auf Waferebene weiter und subventionieren das Marktwachstum.

Nordamerika

Im Jahr 2025 erwirtschaftete Nordamerika 0,53 Milliarden US-Dollar und trug damit 25,30 % zum weltweiten Marktumsatz bei. Bis 2026 wird ein Wachstum auf 0,65 Milliarden US-Dollar prognostiziert. Nordamerika wird voraussichtlich das schnellste Wachstum in der 3D-Stacking-Branche verzeichnen, angetrieben durch die schnelle Einführung fortschrittlicher Technologien in der Region und eine hohe Nachfrage nach effizienten, kompakten Geräten in verschiedenen Sektoren. Wichtige Marktteilnehmer, unterstützt durch erhebliche Investitionen in Forschung und Entwicklung, treiben die Innovation voran. Da fortschrittliche Verpackungen an Bedeutung gewinnen, entwickelt sich Arizona zu einem wichtigen Knotenpunkt für den lebenswichtigen Herstellungsprozess. Folglich arbeiten lokale Regierungen und Unternehmen des privaten Sektors zusammen, um Arizonas Position als führender Anbieter in der Halbleiterfertigung zu stärken. Der US-Markt soll bis 2026 ein Volumen von 0,47 Milliarden US-Dollar erreichen.

- Im Februar 2024,Amkor gab die Genehmigung seiner ausgelagerten Halbleitermontage- und Testanlage (OSAT) in Peoria, Arizona, bekannt. Mit einer Investition von 2 Milliarden US-Dollar zielt die Anlage darauf ab, ein robustes Verpackungszentrum in Arizona zu errichten und gleichzeitig 2.000 neue Arbeitsplätze für die lokale Belegschaft zu schaffen, wodurch die Halbleiterfertigungskapazitäten der Region weiter gestärkt werden.

Die USA sind auf dem 3D-Stacking-Markt von entscheidender Bedeutung, angetrieben durch einflussreiche Technologieunternehmen und starke staatliche Unterstützung. Beispielsweise wurden durch das im Juli 2022 verabschiedete CHIPS-Gesetz vom Geschäftsjahr 2022 bis zum Geschäftsjahr 2027 52,7 Milliarden US-Dollar für Halbleiterinitiativen bereitgestellt, die sich auf die Fertigung sowie Forschung und Entwicklung konzentrieren. Diese Mittel unterstützen die Weiterentwicklung von 3D-Stack-Technologien, die für KI- und maschinelle Lernanwendungen von entscheidender Bedeutung sind, und festigen damit die Führungsposition der USA in der Halbleiterrevolution und dem Chipdesign der nächsten Generation weiter.

Südamerika

Der südamerikanische Markt wird im Prognosezeitraum voraussichtlich eine bescheidene CAGR verzeichnen. Die lokale Regierung hat Maßnahmen ergriffen, um Investitionen in Technologie und Halbleiterfertigung anzuziehen, die Infrastruktur zu verbessern und Anreize für Forschung und Entwicklung im Halbleitersektor zu bieten. Unternehmen wie Rohm Semiconductor und Hitachi High Technologies bauen eine Präsenz in Brasilien auf und tragen zur Entwicklung fortschrittlicher Verpackungsfähigkeiten, einschließlich 3D-Stacking, bei. Auf Lateinamerika entfielen im Jahr 2025 0,18 Milliarden US-Dollar, was 8,80 % des globalen Marktanteils entspricht, und es wird erwartet, dass er im Jahr 2026 0,21 Milliarden US-Dollar erreichen wird.

Europa

Der europäische Markt machte im Jahr 2025 0,42 Milliarden US-Dollar aus, was 20,40 % der globalen Industrie entspricht, und wird im Jahr 2026 voraussichtlich 0,52 Milliarden US-Dollar erreichen. Europa ist bereit, im Prognosezeitraum einen erheblichen Marktanteil zu erobern, angetrieben durch die zunehmende branchenübergreifende Digitalisierung der Region und die wachsende Nachfrage nach elektronischen Geräten. Um den wachsenden Bedarf an fortschrittlicher Elektronik zu decken, investieren Unternehmen in Spitzentechnologien und erweitern ihre Produktionskapazitäten, wodurch Europa zu einem wichtigen Akteur auf dem Markt wird. Der britische Markt soll bis 2026 ein Volumen von 0,10 Milliarden US-Dollar erreichen, während der deutsche Markt bis 2026 ein Volumen von 0,11 Milliarden US-Dollar erreichen soll.

Deutschlands robuste Automobilindustrie, angetrieben durch die Entwicklung von Elektrofahrzeugen (EVs), autonomem Fahren uswErweiterte Fahrerassistenzsysteme (ADAS), befeuert die Nachfrage nach leistungsstarken und energieeffizienten Halbleitern. Diese Anforderungen unterstützen das Wachstum des 3D-Stacks, der die Transistordichte erhöht und die Datenverarbeitung beschleunigt. Darüber hinaus treibt der rasante Fortschritt von Industrie 4.0, unterstützt durch Deutschlands Führungsrolle in der Edge-Computing-Technologie, die zunehmende Implementierung von 3D-gestapelten Chips in industriellen IoT-Systemen voran.

Naher Osten und Afrika

Der Markt im Nahen Osten und Afrika erwirtschaftete im Jahr 2025 0,26 Milliarden US-Dollar, was 12,40 % der globalen Marktlandschaft entspricht, und wird im Jahr 2026 voraussichtlich 0,3 Milliarden US-Dollar erreichen. Der Nahe Osten und Afrika, insbesondere die Vereinigten Arabischen Emirate und Saudi-Arabien, verzeichnen aufgrund der zunehmenden Digitalisierung und Regierungsinitiativen eine moderate CAGR. Im Rahmen seiner Vision 2030-Initiative tätigt Saudi-Arabien erhebliche Investitionen, um lokale Halbleiterfertigungskapazitäten aufzubauen und so die konzentrierte Lieferkette der Region anzugehen. Unterdessen sind die Investitionen der VAE in intelligente StadtDie Infrastruktur steigert die Nachfrage nach fortschrittlichen Halbleiterlösungen, einschließlich 3D-Stack-Technologien, zur Unterstützung von IoT-Geräten und Hochleistungscomputersystemen.

WETTBEWERBSFÄHIGE LANDSCHAFT

Wichtige Akteure der Branche

Marktteilnehmer tätigen aktive F&E-Investitionen und Kooperationsaktivitäten, um sich einen Wettbewerbsvorteil zu verschaffen

Wichtige Marktteilnehmer engagieren sich aktiv in Forschung und Entwicklung, um 3D-Stapeltechnologien zu innovieren und voranzutreiben, wobei der Schwerpunkt auf der Verbesserung der Leistung, der Kostensenkung und der Bewältigung von Fertigungsherausforderungen liegt. Diese Unternehmen gehen außerdem strategische Partnerschaften mit Branchenführern und Forschungseinrichtungen ein, um Fachwissen zu nutzen und die Einführung von 3D-Stack-Lösungen zu beschleunigen.

- Im Februar 2024,Samsung beschleunigte seine 3D-Verpackungskapazitäten durch die Einführung einer Hybrid-Bonding-Produktionslinie in seinem modernen Verpackungszentrum in Korea. Das Unternehmen hat sich mit Applied Materials und Besi Semiconductor zusammengetan, um Hybrid-Bonding-Geräte auf seinem Cheonan Campus zu installieren, einem wichtigen Standort für die Produktion fortschrittlicher Verpackungen.

Lange Liste der untersuchten Unternehmen (einschließlich, aber nicht beschränkt auf)

- Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwan)

- Intel Corporation (USA)

- Samsung Electronics Co., Ltd. (Südkorea)

- Advanced Micro Devices Inc.(UNS.)

- Advanced Semiconductor Engineering Inc. (Taiwan)

- Texas Instruments Inc. (USA)

- Amkor Technology Inc. (USA)

- Tektronix Inc.(UNS.)

- Broadcom Inc. (USA)

- Cadence Design Systems, Inc. (USA)

- IBM Corporation (USA)

- Marvell Technology, Inc. (USA)

- Lightmatter (USA)

- Kioxia Corporation (Japan)

- JCET-Gruppe (China)

- Graphcore(VEREINIGTES KÖNIGREICH.)

….und mehr

WICHTIGE ENTWICKLUNGEN IN DER INDUSTRIE

- Juni 2025:Cadence Design Systems, Inc. hat seine Zusammenarbeit mit Samsung Foundry durch eine mehrjährige IP-Vereinbarung erweitert und die Speicher- und Schnittstellen-IP-Lösungen von Cadence auf die fortschrittlichen Prozessknoten SF5A, SF2P und SF4X von Samsung Foundry ausgeweitet. Diese Partnerschaft verbessert die Multi-Die-Planung und -Implementierung durch das Angebot von Referenzabläufen und Paketdesign-Kits, die auf der Cadence Integrity 3D-IC-Plattform basieren und Paketierung, Analyse auf Systemebene und Systemplanung integrieren.

- Juni 2025:Soitec, ein in Frankreich ansässiges Unternehmen für Halbleitermaterialien, hat eine Zusammenarbeit mit der Powerchip Semiconductor Manufacturing Corporation (PSMC) angekündigt. Im Rahmen der Vereinbarung wird Soitec PSMC mit 300-mm-Substraten mit einer Trennschicht und TLT-Fähigkeit (Transistor Layer Transfer) beliefern und so eine neue Demonstration des fortschrittlichen 3D-Chip-Stackings auf Waferebene unterstützen.

- April 2025:Intel hat im Rahmen seiner aktualisierten Hardware-Roadmap seinen 14A (1,4 nm)-Knoten der nächsten Generation vorgestellt. Das Unternehmen stellte außerdem seine 18A-P- und 18A-PT-Knoten vor. Der 18A-P-Knoten ist eine Hochleistungsvariante des 18A, während der 18A-PT Through Silicon Vias (TSVs) für 3D-Chip-Stacking unterstützt. Die Knoten der T-Serie von Intel integrieren außerdem die Foveros Direct 3D-Technologie, die ähnliche Eigenschaften wie die 3D-Chip-Stacking-Technologie von TSMC aufweist.

- Januar 2025:Samsung Foundry hatte mit Dreambig Semiconductor zusammengearbeitet, um die MARS-Chip-Label-Plattform zu entwickeln und die Chiplets Networking IO und Chiplet Hub einzuführen. Diese Zusammenarbeit nutzt Samsung Foundrys fortschrittliche 3D-Chip-on-Wafer-Stacking- und SF4X-FinFET-Prozesstechnologie. Mit seiner umfassenden Expertise im Bereich HBM-Speicher und synergistischer fortschrittlicher Verpackung arbeitet Samsung Foundry eng mit Dreambig Semiconductor zusammen, um die Fähigkeiten der Plattform weiterzuentwickeln.

- November 2024:Lightmatter, ein photonisches Supercomputing-Unternehmen, gab eine strategische Zusammenarbeit mit Advanced Semiconductor Engineering, Inc. bekannt. Diese Partnerschaft zielt darauf ab, die Passage-Plattform von Lightmatter, eine 3D-gestapelte Photonik-Engine mit steckbarer Glasfaser, weiterzuentwickeln, um die kritischen KI-Verbindungsengpässe zu beheben, die derzeit die Leistung der Rechenzentrumsinfrastruktur einschränken.

- August 2024:TSMC stellte seine 3DFabric-Technologiefamilie vor, einschließlich 2D- und 3D-Frontend- und Backend-Verbindungslösungen. Die TSMC-SoIC-Frontend-Technologien (System on Integrated Chips) implementieren die Präzision und Methoden von Edge-Siliziumfabriken, die für das 3D-Siliziumstapeln unerlässlich sind. Der Die-Stacking-Prozess umfasst Wafer-on-Wafer (WoW)- und Chip-on-Wafer (CoW)-Technologien und ermöglicht das 3D-Stapeln identischer und heterogener Dies.

INVESTITIONSANALYSE UND CHANCEN

Die 3D-Stacking-Branche steht vor einem erheblichen Wachstum, angetrieben durch technologische Fortschritte, strategische Investitionen und unterstützende Regierungsmaßnahmen. Durch die Konzentration auf fortschrittliche Verpackungslösungen, F&E-Initiativen und strategische Partnerschaften können Stakeholder von den neuen Chancen in diesem dynamischen Sektor profitieren. Zum Beispiel,

- Im Juni 2025GlobalFoundries kündigte zusammen mit der Trump-Administration und führenden Technologieunternehmen wie SpaceX, Apple, Qualcomm Technologies, Inc., AMD, GM und NXP Pläne an, 16 Milliarden US-Dollar in die Entwicklung seiner fortschrittlichen Verpackungs- und Halbleiterfertigungskapazitäten in seinen Einrichtungen in Vermont und New York zu investieren, um kritische Komponenten ihrer Lieferkette an Land zu bringen.

BERICHTSBEREICH

Der Bericht bietet eine detaillierte Analyse des Marktes und konzentriert sich auf Schlüsselaspekte wie führende Unternehmen, Produkt-/Dienstleistungstypen und führende Anwendungen des Produkts. Darüber hinaus bietet der Bericht Einblicke in die Markttrends und beleuchtet wichtige Branchenentwicklungen. Zusätzlich zu den oben genannten Faktoren umfasst der Bericht mehrere Faktoren, die zum Wachstum des Marktes in den letzten Jahren beigetragen haben.

Anfrage zur Anpassung um umfassende Marktkenntnisse zu erlangen.

BERICHTSUMFANG UND SEGMENTIERUNG

|

ATTRIBUT |

DETAILS |

|

Studienzeit |

2021-2034 |

|

Basisjahr |

2025 |

|

Geschätztes Jahr |

2026 |

|

Prognosezeitraum |

2026-2034 |

|

Historische Periode |

2021-2024 |

|

Wachstumsrate |

CAGR von19.70% von 2026 bis 2034 |

|

Einheit |

Wert (Milliarden USD) |

|

Segmentierung |

Nach Methode

Durch Technologie

Nach Gerät

Nach Branche

Nach Region

|

|

Im Bericht vorgestellte Unternehmen |

Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwan), Intel Corporation (USA), Samsung Electronics Co., Ltd. (Südkorea), Advanced Micro Devices Inc. (USA), Advanced Semiconductor Engineering Inc. (Taiwan), Texas Instruments Inc. (USA), Amkor Technology Inc. (USA), Tektronix Inc. (USA), Broadcom Inc. (USA), Cadence Design Systems, Inc. (USA) usw. |

Häufig gestellte Fragen

Der Markt soll bis 2034 ein Volumen von 10,51 Milliarden US-Dollar erreichen.

Im Jahr 2025 wurde der Markt auf 2,08 Milliarden US-Dollar geschätzt.

Der Markt wird im Prognosezeitraum voraussichtlich mit einer jährlichen Wachstumsrate von 19,70 % wachsen.

Bezogen auf den Marktanteil ist das 3D-TSV-Segment marktführend.

Der Anstieg der Anforderungen an KI und Rechenzentren treibt das Marktwachstum voran.

Taiwan Semiconductor Manufacturing Company Limited (TSMC), Intel Corporation, Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Advanced Semiconductor Engineering Inc., Cadence Design Systems, Inc. und Texas Instruments Inc. sind die Top-Player auf dem Markt.

Nordamerika wird voraussichtlich den höchsten Marktanteil halten.

Nach Branchen wird erwartet, dass der IT- und Telekommunikationssektor im Prognosezeitraum mit der höchsten CAGR wächst.

Nehmen Sie Kontakt mit unseren Experten auf Sprechen Sie mit einem Experte

20% kostenlose Anpassung erhalten

Regionale und länderspezifische Abdeckung erweitern, Segmentanalyse, Unternehmensprofile, Wettbewerbs-Benchmarking, und Endnutzer-Einblicke.

Verwandte Berichte

-

US +1 833 909 2966 (Gebührenfrei)

-

Nehmen Sie Kontakt mit uns auf