Tamaño del mercado de apilamiento 3D, participación y análisis de la industria, por método (matriz a matriz, matriz a oblea, oblea a oblea, chip a chip y chip a oblea), por tecnología (TSV 3D (a través de silicio vía), enlace híbrido 3D, integración 3D monolítica y otros), por dispositivo (MEMS/sensores, imágenes y optoelectrónica, circuitos integrados lógicos, dispositivos de memoria, LED y otros), por industria (TI y telecomunicaciones, electrónica de consumo, automoción, fabricación, atención sanitaria y otros) y pronóstico regional, 2026 – 2034

INFORMACIÓN CLAVE DEL MERCADO

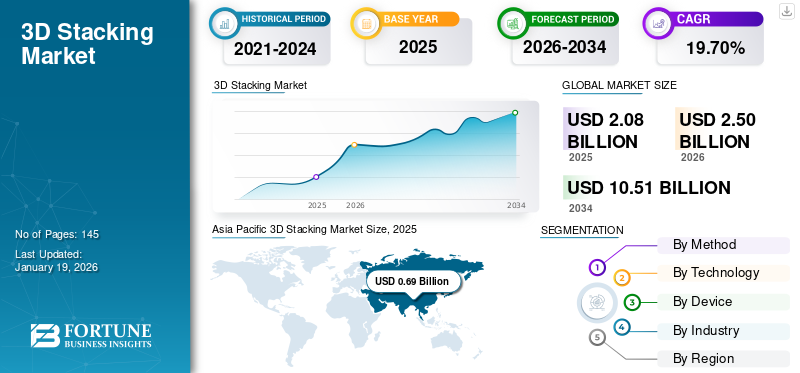

El tamaño del mercado mundial de apilamiento 3D se valoró en USD2.08mil millones en 2025. Se proyecta que el mercado crecerá de USD2.50mil millones en 2026 a USD10.51mil millones para 2034, exhibiendo una tasa compuesta anual de19,70% durante el período de pronóstico.

El apilamiento 3D, también conocido como integración 3D o apilamiento de IC 3D, es una tecnología avanzada de empaquetado de semiconductores que implica el apilamiento vertical de múltiples capas de circuitos integrados (CI) o troqueles en un solo paquete compacto. Estas capas apiladas están interconectadas mediante Through-Silicon Vias (TSV), micro-bumps o unión de oblea a oblea/chip a oblea, lo que permite una transferencia de datos más rápida y un rendimiento mejorado.

La rápida expansión de las aplicaciones de semiconductores en diversas industrias y la integración de la electrónica avanzada en el sector automotriz indican importantes oportunidades que se avecinan para el crecimiento del mercado. Además, la creciente adopción de la tecnología de pila 3D para proporcionar interconexiones más cortas y reducir el consumo de energía subsidia aún más el crecimiento del mercado. Esta tecnología permite un procesamiento de datos más rápido y reduce la latencia, lo que promueve el análisis de datos, el aprendizaje automático ycomputación en la nube.

Diferentes empresas que operan en el mercado, incluidas Taiwan Semiconductor Manufacturing Company Limited (TSMC), Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Cadence Design Systems, Inc., Texas Instruments Inc. y otras. Estos actores han adoptado varias estrategias para fortalecer sus posiciones en el mercado y aumentar la penetración del mercado en la industria del apilamiento 3D. Por ejemplo,

- En septiembre de 2024,Samsung anunció sus planes para producir en masa System-on-Chip (SoC) apilado en 3D en 2026. La compañía tiene como objetivo mejorar el rendimiento y abordar los desafíos de la miniaturización de semiconductores apilando semiconductores con diferentes funcionalidades.

Elindustria de semiconductoreses sensible a las interrupciones de la cadena de suministro global, como se vio durante la pandemia de COVID-19. La demanda causada por la pandemia había puesto a prueba la capacidad en todos los puntos de la cadena de suministro, empezando por los proveedores de componentes. La pandemia de COVID-19 impulsó la escasez de chips, y sus impactos de largo alcance, incluidos brotes de virus, desafíos laborales e incertidumbres geopolíticas, la han alimentado. Esto había obstaculizado temporalmente el crecimiento del mercado; sin embargo, se espera que la industria alcance sus niveles previos a la pandemia en los próximos años.

Descargar muestra gratuita para conocer más sobre este informe.

IMPACTO DE LA IA GENERATIVA

Adopción de IA generativa para acelerar el proceso de diseño y simulación para impulsar la expansión del mercado

La IA generativa influye significativamente en la expansión del mercado, particularmente en el sector de los semiconductores. Este impacto es evidente en varios campos, incluida la innovación en el diseño, la eficiencia de la fabricación y la dinámica del mercado.

La IA generativa mejora la fase de diseño de la pila 3D al automatizar la creación de diseños y simulaciones mejorados. Las herramientas que incluyen algoritmos de diseño generativo permiten a los ingenieros explorar diversas posibilidades de diseño, lo que lleva a arquitecturas apiladas en 3D más eficientes e innovadoras. Esta aceleración en los procesos de diseño es crucial ya que la industria busca satisfacer las crecientes necesidades de aplicaciones comointeligencia artificial (IA)y computación de alto rendimiento.

DINÁMICA DEL MERCADO

Tendencias del mercado de apilamiento 3D

Avances en las tecnologías de envasado de chips para impulsar el crecimiento del mercado

Las diversas aplicaciones de las tecnologías de apilamiento 3D impulsan el crecimiento del mercado de apilamiento 3D. Plataformas clave como 3D NAND, 3D SoC y CBA DRAM, junto con tecnologías que incluyen la memoria apilada 3D, desempeñan un papel crucial a la hora de abordar los requisitos de potencia, miniaturización y rendimiento de la electrónica moderna. Los diseños basados en chiplets y la integración heterogénea están remodelando la arquitectura de semiconductores. Los principales actores de la industria, incluidos Intel, TSMC, Nvidia y AMD, están invirtiendo sustancialmente en estas soluciones, mediante el uso de enlaces híbridos para mejorar los lanzamientos de interconexión.

En los próximos años tendencias como el 3.5Dembalajey se espera que el embalaje a nivel de panel influya significativamente en el mercado, impulsado por la creciente demanda de soluciones informáticas y de inteligencia artificial de alto rendimiento. El panorama competitivo está cambiando a medida que las fundiciones y las IDM mejoran sus capacidades de envasado, mientras que los nuevos participantes de China intensifican la competencia. Con la miniaturización de chips tradicional acercándose a sus límites físicos, la industria está adoptando progresivamente técnicas de empaquetado avanzadas para mejorar el rendimiento y la integración.

Impulsores del mercado

El aumento de la demanda de inteligencia artificial y centros de datos impulsa el crecimiento del mercado

La demanda de centros de datos ya ha aumentado debido a la creciente importancia de los datos en el mundo actual. Sin embargo, se espera que esta demanda crezca aún más con el aumento deIA generativa (gen AI). La tecnología de apilamiento de chips 3D tiene un impacto positivo en los centros de datos y abre nuevas oportunidades para la optimización de costos.

La infraestructura de los centros de datos en todo el mundo está evolucionando rápidamente para admitir capacidades de IA, lo que permite el procesamiento de grandes volúmenes de cálculos y requisitos complejos. Las regiones de Asia Pacífico y América del Norte lideran actualmente la proliferación de centros de datos, con centros clave en ciudades como Beijing, Shanghai, el norte de Virginia y el Área de la Bahía de San Francisco. Según un informe de 2024 del IBM Institute for Business Value (IBM IBV), el 43% de los ejecutivos de tecnología de nivel C han expresado crecientes preocupaciones sobre su infraestructura tecnológica en los últimos seis meses debido al aumento de la IA generativa, lo que les permite centrarse en optimizar su infraestructura para satisfacer sus necesidades de escala.

Las inversiones notables de las principales empresas de tecnología también indican un fuerte crecimiento para el sector de los centros de datos de IA. En 2025, Microsoft pretende invertir alrededor de 80 mil millones de dólares en la construcción de un centro de datos, mientras que Meta dedica 10 mil millones de dólares a una nueva hiperescala de cuatro millones de pies cuadrados.centro de datosproyecto en Luisiana.

Desafíos del mercado

Las complejidades de fabricación y el aumento de costos obstaculizan el avance del mercado de apilamiento 3D

Uno de los desafíos clave en la implementación del apilamiento de chips 3D es la mayor complejidad de fabricación. El proceso exige técnicas de fabricación avanzadas y equipos altamente especializados, lo que puede aumentar significativamente los costos de producción. Además, esta complejidad puede generar problemas de rendimiento, lo que afectará aún más la competencia y eficacia de fabricación.

Además, los materiales esenciales para la pila 3D, como intercaladores de silicio, vías a través de silicio (TSV) y microprotuberancias de paso fino, contribuyen a elevar los costos de producción. Estos componentes requieren procesos de fabricación sofisticados, lo que aumenta los gastos en materiales y procesos. Garantizar la compatibilidad con las arquitecturas de hardware, las interfaces de software y los sistemas de gestión térmica existentes a menudo requiere una inversión significativa y modificaciones a nivel del sistema. Como resultado, estos desafíos pueden frenar la adopción más amplia de tecnologías de pila 3D.

Descargar muestra gratuita para conocer más sobre este informe.

Oportunidades de mercado

Iniciativas e inversiones gubernamentales activas para atender nuevas vías de crecimiento

Los programas gubernamentales, incluida la Ley de Ciencia y CHIPS de EE. UU., están facilitando importantes inversiones en la fabricación de semiconductores. Estas iniciativas tienen como objetivo mejorar las capacidades de producción nacional y reducir la dependencia de las cadenas de suministro extranjeras, creando oportunidades para crecer.embalaje avanzadotecnologías, incluido el apilamiento 3D. Por ejemplo,

- En junio de 2025,Micron Technology Inc. anunció una inversión histórica de aproximadamente 200 mil millones de dólares en fabricación e I+D con sede en Estados Unidos, lo que subraya los esfuerzos de Estados Unidos por recuperar el liderazgo en la industria mundial de semiconductores. Esta expansión cuenta con un respaldo significativo del gobierno de EE. UU., y se espera que Micron reciba alrededor de 6.500 millones de dólares en apoyo en virtud de la Ley CHIPS y Ciencia.

Además, importantes inversiones realizadas por líderes de la industria, como la instalación de empaquetado de chips de TSMC por valor de 2.900 millones de dólares y la expansión de 110 millones de dólares de Fujifilm en capacidades de pulido de chips, resaltan el compromiso continuo de Taiwán con el avance de la excelencia en semiconductores.

ANÁLISIS DE SEGMENTACIÓN

Por método

El apilamiento 3D de matriz a oblea para una solución de chip personalizada impulsa el crecimiento segmentario

Según el método, el mercado se segmenta en matriz a matriz, matriz a oblea, oblea a oblea, chip a chip y chip a oblea.

Se espera que el método de matriz en oblea obtenga la mayor participación de mercado, representando el 28,08% en 2026, debido a su capacidad para satisfacer las demandas de envases de semiconductores confiables, rentables y de alto rendimiento. El método D2W permite integrar diferentes tipos de troqueles (por ejemplo, lógicos, de memoria,sensores) en un solo paquete. Esto es importante para las aplicaciones en evolución que necesitan soluciones de chips personalizadas, como AI, 5G e IoT, aumentando así el mercado potencial para las tecnologías de pila 3D. Por ejemplo,

- En mayo de 2025,SUSS, un proveedor global de soluciones de procesos y equipos de semiconductores, lanzó la plataforma XBC300 Gen2 D2W, una solución de unión avanzada que mejora su cartera de unión híbrida. Esta nueva plataforma admite la unión de matriz a oblea (D2W) en sustratos de 200 mm y 300 mm, lo que aborda los estrictos requisitos de espaciado entre matrices y permite una integración de alta precisión para dispositivos semiconductores de próxima generación.

Sin embargo, se prevé que el método de oblea a oblea experimente la CAGR más alta durante el período de pronóstico. Las conexiones de oblea a oblea exhiben un rápido crecimiento a través de sus puntos de interconexión en miniatura y ofertas de fabricación de alto rendimiento, lo que las hace ideales para la incorporación de memoria, aplicaciones de procesamiento neuromórfico y tecnologías de sensores de imagen.

Por tecnología

La creciente adopción de 3D TSV para soluciones de embalaje avanzadas cataliza el crecimiento segmentario

Según la tecnología, el mercado se segmenta en 3D TSV (a través de Silicon Via), unión híbrida 3D, integración 3D monolítica y otros.

En 2026, se espera que la tecnología 3D TSV (Through-Silicon Via) tenga la mayor cuota de mercado, representando el 33,92%. destacando su papel fundamental en el apoyo a la integración vertical dentro de los dispositivos semiconductores. Los TSV funcionan como conexiones eléctricas verticales, lo que facilita la creación de paquetes 3D innovadores y circuitos integrados al vincular directamente matrices semiconductoras apiladas. Esta táctica elimina la necesidad de cableado de borde convencional o unión de cables, que se usaba anteriormente en paquetes apilados sobre sustratos orgánicos. Debido a su rendimiento superior y capacidades de integración compacta, los TSV se prefieren gradualmente en la fabricación de equipos de última generación.Circuitos integrados 3Dy arquitecturas basadas en intercaladores.

Se espera que los enlaces híbridos 3D registren la CAGR más alta durante el período previsto, impulsada por el aumento de las inversiones en tecnologías avanzadas de apilamiento de chips. Este método de unión conecta interfaces metal con metal y dieléctrico a dieléctrico, lo que reduce considerablemente la resistencia de interconexión y mejora la integridad de la señal. Como resultado, ofrece eficiencia energética, rendimiento y escalabilidad superiores, requisitos clave para aceleradores de IA, procesadores de computación de alto rendimiento (HPC) y soluciones de memoria de alta velocidad.

Por dispositivo

Aumento de la demanda de memoria de alto ancho de banda (HBM) para impulsar la expansión del segmento de dispositivos de memoria

Por dispositivo, el mercado se divide en MEMS/sensores, imágenes y optoelectrónica, circuitos integrados lógicos, dispositivos de memoria, LED y otros.

Se espera que los dispositivos de memoria sean fundamentales para impulsar el mercado de apilamiento 3D, representando una participación del 27,37% en 2026, impulsado por la creciente demanda de mayor rendimiento, mayor densidad y factores de forma compactos. El aumento de las aplicaciones con uso intensivo de datos, como la inteligencia artificial (IA), la computación en la nube y la computación de alto rendimiento (HPC), ha acelerado la adopción de soluciones de memoria apilada en 3D, incluidas 3D NAND, memoria de alto ancho de banda (HBM) y DRAM avanzada. En respuesta a la creciente necesidad de memoria rápida y de baja latencia, empresas líderes como Samsung, Micron y SK Hynix están invirtiendo considerablemente en apilamiento 3D NAND y tecnologías HBM basadas en TSV para mejorar la densidad de la memoria y al mismo tiempo mejorar la eficacia energética.

Se espera que los circuitos integrados lógicos registren la CAGR más alta entre 2025 y 2032. Las crecientes cargas de trabajo informáticas heterogéneas,aprendizaje automático (ML)La complejidad y la inteligencia artificial (IA) están impulsando la demanda de circuitos integrados lógicos apilados en 3D, específicamente para FPGA, aceleradores y procesadores de IA. Por ejemplo,

- En agosto de 2024,Powerchip Semiconductor Manufacturing Company (PSMC) presentó sus interposers 2.5D con tecnología de apilamiento de obleas multicapa Logic-DRAM, para abordar las crecientes demandas de las aplicaciones de IA. Según la compañía, los principales actores, incluido AMD, planean aprovechar esta tecnología con nodos lógicos avanzados de fundiciones líderes para desarrollar chips de IA 3D de alta capacidad, bajo consumo y gran ancho de banda.

Por industria

Para saber cómo nuestro informe puede ayudar a optimizar su negocio, Hable con un analista

La creciente infraestructura de red 5G y la necesidad de soluciones de baja latencia para impulsar la adopción del apilamiento 3D en TI y telecomunicaciones

Por industria, el mercado se segmenta en TI ytelecomunicaciones, electrónica de consumo, automoción, fabricación, atención sanitaria y otros.

Se proyecta que el sector de TI y telecomunicaciones crecerá con una CAGR más alta durante el período de pronóstico, impulsado por el rápido crecimiento en el consumo de datos, el aumento de 5G y la tecnología relacionada, y la creciente necesidad de soluciones de semiconductores de alto rendimiento, compactas y energéticamente eficientes. El despliegue de redes 5G es uno de los principales impulsores de la creciente adopción de la tecnología de pila 3D en el sector de las telecomunicaciones. Dado que 5G requiere mayores velocidades de datos, baja latencia y una comunicación más eficiente entre los nodos de la red, los semiconductores apilados en 3D ofrecen las mejoras de rendimiento necesarias.

- En junio de 2025,Soitec, proveedor de materiales semiconductores, anunció una asociación estratégica con Powerchip Semiconductor Manufacturing Company (PSMC). En el marco de esta colaboración, Soitec acuerda suministrar a PSMC sustratos de 300 mm con una capa de liberación y preparación para transferencia de capa de transistor (TLT). Esto respaldará el apilamiento avanzado de chips 3D a nivel de oblea, mostrando el potencial de las tecnologías de semiconductores de próxima generación.

Elindustria de la electrónica de consumotuvo la mayor participación de mercado en 2024, impulsada por la creciente adopción de tabletas de alto rendimiento, dispositivos portátiles inteligentes y teléfonos inteligentes integrados con capacidades AR/VR. Estos dispositivos exigen procesamiento de alta velocidad y eficiencia energética y soluciones compactas de memoria apilada 3D de consumo, como 3D NAND y HBM, junto con circuitos integrados lógicos avanzados, para mejorar la duración de la batería y el rendimiento completo del dispositivo.

PERSPECTIVA REGIONAL DEL MERCADO DE APILAMIENTO 3D

Geográficamente, el mercado se estudia en Asia Pacífico, América del Norte, América del Sur, Europa y Oriente Medio y África.

Asia Pacífico

Asia Pacific 3D Stacking Market Size, 2025 (USD Billion)

Para obtener más información sobre el análisis regional de este mercado, Descargar muestra gratuita

Asia Pacífico dominó el mercado con una valoración de 690 millones de dólares en 2025 y se prevé que alcance los 820 millones de dólares en 2026. Asia Pacífico tuvo la mayor participación en el mercado de apilamiento 3D en 2024, impulsada por las ventajas competitivas de la región. Estos incluyen la disponibilidad de mano de obra barata en China, las continuas innovaciones de las plantas de fabricación en Taiwán, las sólidas capacidades de fabricación de las empresas japonesas y el establecimiento de nuevas fábricas de semiconductores en China, Taiwán, Japón y Corea del Sur. Se prevé que el mercado de Japón alcance los 190 millones de dólares en 2026, el mercado de China alcance los 230 millones de dólares en 2026 y el mercado de la India alcance los 110 millones de dólares en 2026.

El apoyo del gobierno está acelerando aún más el crecimiento del mercado en Asia Pacífico. La inversión de 11.600 millones de dólares de Japón en el desarrollo de tecnología de semiconductores en 2023, de los cuales el 30% se destinará a embalajes avanzados y apilamiento 3D, está impulsando considerablemente la expansión de la industria. De manera similar, el compromiso de Corea del Sur de 427 mil millones de dólares en inversiones en semiconductores para 2030 (Ministerio de Comercio, Industria y Energía) está fortaleciendo el ecosistema de semiconductores de la región.

El mercado chino tuvo la mayor cuota de mercado en la región de Asia Pacífico en 2024. El crecimiento del mercado está impulsado principalmente por la rápida expansión de la fabricación nacional de semiconductores, respaldada por iniciativas gubernamentales, incluido el plan "Hecho en China 2025" de China. Además, el liderazgo del país en aplicaciones de IA e IoT, que dependen en gran medida de una integración heterogénea y una memoria de gran ancho de banda (HBM), está impulsando la demanda. El aumento de la necesidad deConjuntos de chips 5G, procesadores de IA y electrónica para vehículos autónomos acelera aún más la adopción de una integración 3D avanzada a nivel de oblea, subsidiando el crecimiento del mercado.

América del norte

En 2025, América del Norte generó 530 millones de dólares, lo que contribuyó con el 25,30 % a los ingresos del mercado global, y se prevé que crezca a 650 millones de dólares en 2026. Se espera que América del Norte experimente el crecimiento más rápido en la industria del apilamiento 3D, impulsado por la rápida adopción de tecnologías avanzadas en la región y una alta demanda de dispositivos compactos y eficientes en varios sectores. Los actores clave del mercado, respaldados por importantes inversiones en investigación y desarrollo, están impulsando la innovación. A medida que los envases avanzados ganan importancia, Arizona emerge como un centro fundamental para el vital proceso de fabricación. En consecuencia, los gobiernos locales y las empresas del sector privado están colaborando para reforzar la posición de Arizona como líder en la fabricación de semiconductores. Se prevé que el mercado estadounidense alcance los 470 millones de dólares en 2026. Por ejemplo,

- En febrero de 2024,Amkor anunció la aprobación de su instalación subcontratada de prueba y ensamblaje de semiconductores (OSAT) en Peoria, Arizona. Con una inversión de 2.000 millones de dólares, la instalación pretende establecer un sólido centro de embalaje en Arizona y al mismo tiempo crear 2.000 nuevos puestos de trabajo para la fuerza laboral local, reforzando aún más las capacidades de fabricación de semiconductores de la región.

Estados Unidos es esencial en el mercado de apilamiento 3D, impulsado por empresas tecnológicas influyentes y un fuerte apoyo gubernamental. Por ejemplo, la Ley CHIPS, aprobada en julio de 2022, asignó 52.700 millones de dólares a iniciativas de semiconductores desde el año fiscal 2022 hasta el año fiscal 2027, dedicadas a la fabricación y la investigación y el desarrollo. Estos fondos respaldan el avance de las tecnologías de pila 3D fundamentales para las aplicaciones de inteligencia artificial y aprendizaje automático, consolidando aún más a Estados Unidos como líder en la revolución de los semiconductores y el diseño de chips de próxima generación.

Sudamerica

Es probable que el mercado sudamericano registre una CAGR modesta durante el período de pronóstico. El gobierno local ha estado ejecutando políticas para atraer inversiones en tecnología y fabricación de semiconductores, mejorando la infraestructura y ofreciendo incentivos para la investigación y el desarrollo en el sector de los semiconductores. Empresas como Rohm Semiconductor e Hitachi High Technologies están estableciendo presencia en Brasil, contribuyendo al desarrollo de capacidades avanzadas de embalaje, incluido el apilamiento 3D. América Latina representó 180 millones de dólares en 2025, lo que representa el 8,80% de la cuota de mercado mundial, y se prevé que alcance los 210 millones de dólares en 2026.

Europa

El mercado europeo representó 420 millones de dólares en 2025, lo que representa el 20,40 % de la industria mundial, y se espera que alcance los 520 millones de dólares en 2026. Europa está preparada para capturar una cuota de mercado significativa durante el período previsto, impulsada por la creciente digitalización de la región en todas las industrias y la creciente demanda de dispositivos electrónicos. Para satisfacer la creciente necesidad de electrónica avanzada, las empresas invierten en tecnologías de vanguardia y amplían sus capacidades de producción, lo que convierte a Europa en un actor clave en el mercado. Se prevé que el mercado del Reino Unido alcance los 100 millones de dólares en 2026, mientras que el mercado de Alemania alcance los 110 millones de dólares en 2026.

La sólida industria automotriz de Alemania, impulsada por el desarrollo de vehículos eléctricos (EV), la conducción autónoma ySistemas avanzados de asistencia al conductor (ADAS), está impulsando la demanda de semiconductores de alto rendimiento y eficiencia energética. Estos requisitos respaldan el crecimiento de la pila 3D, que mejora la densidad de los transistores y acelera el procesamiento de datos. Además, el rápido avance de la Industria 4.0, impulsado por el liderazgo de Alemania en tecnología de computación de punta, está impulsando una mayor implementación de chips apilados en 3D en sistemas industriales de IoT.

Medio Oriente y África

El mercado de Oriente Medio y África generó 260 millones de dólares en 2025, lo que representa el 12,40 % del panorama del mercado mundial, y se espera que alcance los 300 millones de dólares en 2026. Oriente Medio y África, en particular los Emiratos Árabes Unidos y Arabia Saudita, están experimentando una CAGR moderada impulsada por una creciente digitalización e iniciativas gubernamentales. Como parte de su iniciativa Visión 2030, Arabia Saudita está realizando inversiones notables para establecer capacidades locales de fabricación de semiconductores, abordando la cadena de suministro concentrada de la región. Mientras tanto, la inversión de los EAU en ciudad inteligenteLa infraestructura está impulsando la demanda de soluciones avanzadas de semiconductores, incluidas tecnologías de pila 3D, para respaldar dispositivos IoT y sistemas informáticos de alto rendimiento.

PAISAJE COMPETITIVO

Actores clave de la industria

Los actores del mercado realizan inversiones activas en I+D y actividades de colaboración para obtener una ventaja competitiva

Los actores clave del mercado participan activamente en I+D para innovar y hacer avanzar las tecnologías de apilamiento 3D, centrándose en mejorar el rendimiento, reducir costos y abordar los desafíos de fabricación. Estas empresas también establecen asociaciones estratégicas con líderes de la industria e instituciones de investigación para aprovechar la experiencia y acelerar la adopción de soluciones de pila 3D.

- En febrero de 2024,Samsung aceleró sus capacidades de embalaje 3D con el lanzamiento de una línea de producción de unión híbrida en su centro de embalaje avanzado en Corea. La empresa se ha asociado con Applied Materials y Besi Semiconductor para instalar equipos de unión híbrida en su campus de Cheonan, un sitio fundamental para la producción de envases avanzados.

Lista larga de empresas estudiadas (incluidas, entre otras)

- Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwán)

- Corporación Intel (EE.UU.)

- Samsung Electronics Co., Ltd. (Corea del Sur)

- Micro dispositivos avanzados Inc.(A NOSOTROS.)

- Advanced Semiconductor Engineering Inc. (Taiwán)

- Texas Instruments Inc. (EE.UU.)

- Amkor Technology Inc. (EE. UU.)

- Tektronix Inc.(A NOSOTROS.)

- Broadcom Inc. (EE.UU.)

- Cadence Design Systems, Inc. (EE. UU.)

- Corporación IBM (EE.UU.)

- Marvell Technology, Inc. (EE. UU.)

- Materia ligera (EE. UU.)

- Corporación Kioxia (Japón)

- Grupo JCET (China)

- núcleo gráfico(Reino Unido)

….y más

DESARROLLOS CLAVE DE LA INDUSTRIA

- Junio de 2025:Cadence Design Systems, Inc. ha ampliado su colaboración con Samsung Foundry a través de un acuerdo IP de varios años, ampliando las soluciones IP de interfaz y memoria de Cadence a través de los nodos de proceso avanzado SF5A, SF2P y SF4X de Samsung Foundry. Esta asociación mejora la planificación e implementación de múltiples troqueles al ofrecer flujos de referencia y kits de diseño de paquetes, construidos en la plataforma Cadence Integrity 3D-IC, que integra empaquetamiento, análisis a nivel de sistema y planificación de sistemas.

- Junio de 2025:Soitec, una empresa de materiales semiconductores con sede en Francia, ha anunciado una colaboración con Powerchip Semiconductor Manufacturing Corporation (PSMC). Como parte del acuerdo, Soitec suministrará a PSMC sustratos de 300 mm con una capa de liberación y preparación para transferencia de capa de transistor (TLT), lo que respaldará una nueva demostración de apilamiento avanzado de chips 3D a nivel de oblea.

- Abril de 2025:Intel ha presentado su nodo 14A (1,4 nm) de próxima generación como parte de su hoja de ruta de hardware actualizada. La empresa también presentó sus nodos 18A-P y 18A-PT. El nodo 18A-P es una variante de alto rendimiento del 18A, mientras que el 18A-PT admite Through Silicon Vias (TSV) para el apilamiento de chips 3D. Los nodos de la serie T de Intel también integran la tecnología Foveros Direct 3D, que comparte características similares a las de la tecnología de apilamiento de chips 3D de TSMC.

- Enero de 2025:Samsung Foundry se había asociado con Dreambig Semiconductor para desarrollar la plataforma de etiquetas de chip MARS, presentando los chiplets Networking IO y Chiplet Hub. Esta colaboración aprovecha el avanzado apilamiento 3D de chip en oblea y la tecnología de proceso SF4X FinFET de Samsung Foundry. Con su amplia experiencia en memorias HBM y empaques avanzados sinérgicos, Samsung Foundry trabaja en estrecha colaboración con Dreambig Semiconductor para mejorar las capacidades de la plataforma.

- Noviembre de 2024:Lightmatter, una empresa de supercomputación fotónica, anunció una colaboración estratégica con Advanced Semiconductor Engineering, Inc. Esta asociación tiene como objetivo hacer avanzar la plataforma Passage de Lightmatter, un motor fotónico apilado en 3D con fibra conectable, para abordar los cuellos de botella críticos de interconexión de IA que actualmente limitan el rendimiento de la infraestructura del centro de datos.

- Agosto de 2024:TSMC presentó su familia de tecnologías 3DFabric, incluidas soluciones de interconexión frontend y backend 2D y 3D. Las tecnologías frontend TSMC-SoIC (Sistema en chips integrados) implementan la precisión y las metodologías de las fábricas de silicio de borde, esenciales para el apilamiento de silicio 3D. El proceso de apilamiento de troqueles incorpora tecnologías Wafer-on-Wafer (WoW) y Chip-on-Wafer (CoW), que permiten el apilado 3D de troqueles idénticos y heterogéneos.

ANÁLISIS DE INVERSIÓN Y OPORTUNIDADES

La industria del apilamiento 3D está preparada para un crecimiento sustancial, impulsado por avances tecnológicos, inversiones estratégicas y políticas gubernamentales de apoyo. Al centrarse en soluciones de embalaje avanzadas, iniciativas de I+D y asociaciones estratégicas, las partes interesadas pueden aprovechar las oportunidades emergentes en este sector dinámico. Por ejemplo,

- En junio de 2025,GlobalFoundries, junto con la Administración Trump y empresas tecnológicas líderes como SpaceX, Apple, Qualcomm Technologies, Inc., AMD, GM y NXP, con el objetivo de incorporar componentes críticos de su cadena de suministro, anunciaron planes para invertir 16 mil millones de dólares para desarrollar sus capacidades avanzadas de fabricación de semiconductores y envases en sus instalaciones de Vermont y Nueva York.

COBERTURA DEL INFORME

El informe proporciona un análisis detallado del mercado y se centra en aspectos clave como empresas líderes, tipos de productos/servicios y aplicaciones líderes del producto. Además, el informe ofrece información sobre las tendencias del mercado y destaca desarrollos clave de la industria. Además de los factores anteriores, el informe abarca varios factores que contribuyeron al crecimiento del mercado en los últimos años.

Solicitud de personalización para obtener un conocimiento amplio del mercado.

ALCANCE Y SEGMENTACIÓN DEL INFORME

|

ATRIBUTO |

DETALLES |

|

Período de estudio |

2021-2034 |

|

Año base |

2025 |

|

Año estimado |

2026 |

|

Período de pronóstico |

2026-2034 |

|

Período histórico |

2021-2024 |

|

Índice de crecimiento |

CAGR de19,70% de 2026 a 2034 |

|

Unidad |

Valor (millones de dólares) |

|

Segmentación |

Por método

Por tecnología

Por dispositivo

Por industria

Por región

|

|

Empresas perfiladas en el informe |

Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwán), Intel Corporation (EE. UU.), Samsung Electronics Co., Ltd. (Corea del Sur), Advanced Micro Devices Inc. (EE. UU.), Advanced Semiconductor Engineering Inc. (Taiwán), Texas Instruments Inc. (EE. UU.), Amkor Technology Inc. (EE. UU.), Tektronix Inc. (EE. UU.), Broadcom Inc. (EE. UU.), Cadence Design Systems, Inc. (EE. UU.), etc. |

Preguntas frecuentes

Se prevé que el mercado alcance los 10.510 millones de dólares en 2034.

En 2025, el mercado estaba valorado en 2.080 millones de dólares.

Se prevé que el mercado crezca a una tasa compuesta anual del 19,70% durante el período previsto.

En términos de cuota de mercado, el segmento 3D TSV lidera el mercado.

El aumento de la demanda de centros de datos e inteligencia artificial impulsa el crecimiento del mercado.

Taiwan Semiconductor Manufacturing Company Limited (TSMC), Intel Corporation, Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Advanced Semiconductor Engineering Inc., Cadence Design Systems, Inc., Texas Instruments Inc., son los principales actores del mercado.

Se espera que América del Norte tenga la mayor cuota de mercado.

Por industria, se espera que el sector de TI y telecomunicaciones crezca con una CAGR más alta durante el período de pronóstico.

Póngase en contacto con nuestras expertas Habla con un experto

Obtenga un 20% de personalización gratuita

Ampliar la cobertura regional y por país, Análisis de segmentos, Perfiles de empresas, Benchmarking competitivo, e información sobre el usuario final.

Informes relacionados