Tamanho do mercado de empilhamento 3D, análise de participação e indústria, por método (Die-to-Die, Die-to-Wafer, Wafer-to-Wafer, Chip-to-Chip e Chip-to-Wafer), por tecnologia (3D TSV (através de silício via), ligação híbrida 3D, integração 3D monolítica e outros), por dispositivo (MEMS/sensores, imagem e optoeletrônica, ICs lógicos, memória Dispositivos, LEDs e outros), por setor (TI e telecomunicações, eletrônicos de consumo, automotivo, manufatura, saúde e outros) e previsão regional, 2026 – 2034

PRINCIPAIS INFORMAÇÕES DE MERCADO

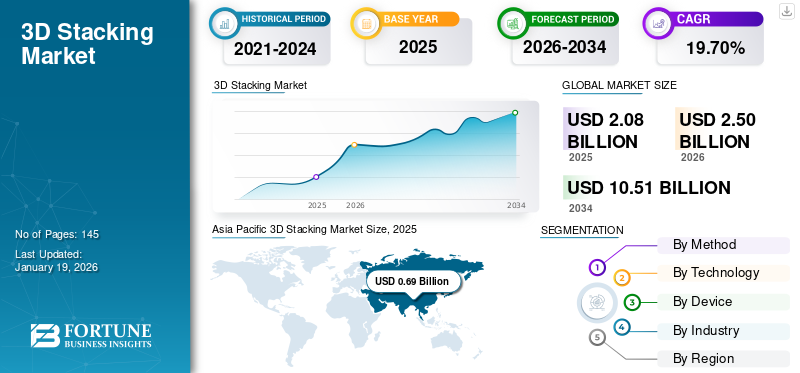

O tamanho do mercado global de empilhamento 3D foi avaliado em dólares americanos2.08bilhões em 2025. O mercado deverá crescer de USD2,50bilhões em 2026 para dólares americanos10.51bilhão até 2034, exibindo um CAGR de19h70% durante o período de previsão.

O empilhamento 3D, também conhecido como integração 3D ou empilhamento 3D IC, é uma tecnologia avançada de empacotamento de semicondutores que envolve o empilhamento vertical de múltiplas camadas de circuitos integrados (ICs) ou matrizes em um único pacote compacto. Essas camadas empilhadas são interconectadas usando Through-Silicon Vias (TSVs), micro-bumps ou ligação wafer-to-wafer/chip-to-wafer, permitindo transferência de dados mais rápida e melhor desempenho.

A rápida expansão das aplicações de semicondutores em diversas indústrias e a integração de eletrônica avançada no setor automotivo indicam grandes oportunidades que estão por vir para o crescimento do mercado. Além disso, a crescente adoção da tecnologia de pilha 3D para fornecer interconexões mais curtas e reduzir o consumo de energia subsidia ainda mais o crescimento do mercado. Essa tecnologia permite um processamento de dados mais rápido e diminui a latência, promovendo análise de dados, aprendizado de máquina ecomputação em nuvem.

Diferentes empresas que operam no mercado, incluindo Taiwan Semiconductor Manufacturing Company Limited (TSMC), Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Cadence Design Systems, Inc., Texas Instruments Inc., entre outras. Esses players adotaram diversas estratégias para fortalecer suas posições de mercado e aumentar a penetração de mercado na indústria de empilhamento 3D. Por exemplo,

- Em setembro de 2024,A Samsung anunciou seus planos de produzir em massa System-on-Chip (SoC) 3D empilhado em 2026. A empresa pretende melhorar o desempenho e enfrentar os desafios da miniaturização de semicondutores, empilhando semicondutores com diferentes funcionalidades.

Oindústria de semicondutoresé sensível às perturbações da cadeia de abastecimento global, como se viu durante a pandemia da COVID-19. A procura causada pela pandemia sobrecarregou a capacidade em todos os pontos da cadeia de abastecimento, começando pelos fornecedores de componentes. A pandemia da COVID-19 deu início à escassez de chips, e os seus impactos de longo alcance, incluindo surtos de vírus, desafios laborais e incertezas geopolíticas, alimentaram-na. Isto prejudicou temporariamente o crescimento do mercado; no entanto, espera-se que a indústria atinja os níveis pré-pandemia nos próximos anos.

Descarregue amostra grátis para saber mais sobre este relatório.

IMPACTO DA IA GERATIVA

Adoção de IA generativa para acelerar o processo de design e simulação para impulsionar a expansão do mercado

A IA generativa influencia significativamente a expansão do mercado, particularmente no setor de semicondutores. Este impacto é evidente em vários campos, incluindo inovação em design, eficiência de produção e dinâmica de mercado.

A IA generativa melhora a fase de design da pilha 3D, automatizando a criação de layouts e simulações aprimorados. Ferramentas que incluem algoritmos de projeto generativos permitem que os engenheiros explorem diversas possibilidades de projeto, levando a arquiteturas empilhadas 3D mais eficientes e inovadoras. Esta aceleração nos processos de design é crucial à medida que a indústria procura atender às crescentes necessidades de aplicações comointeligência artificial (IA)e computação de alto desempenho.

DINÂMICA DE MERCADO

Tendências de mercado de empilhamento 3D

Avanços em tecnologias de embalagem de chips para impulsionar o crescimento do mercado

As diversas aplicações das tecnologias de pilha 3D impulsionam o crescimento do mercado de empilhamento 3D. Plataformas importantes como 3D NAND, 3D SoC e CBA DRAM, juntamente com tecnologias que incluem memória empilhada 3D, desempenham um papel crucial no atendimento aos requisitos de potência, miniaturização e desempenho da eletrônica moderna. Projetos baseados em chips e integração heterogênea estão remodelando a arquitetura de semicondutores. Os principais participantes da indústria, incluindo Intel, TSMC, Nvidia e AMD, estão investindo substancialmente nessas soluções, utilizando ligações híbridas para melhorar os campos de interconexão.

Nos próximos anos, tendências como 3.5Dembalageme espera-se que as embalagens em nível de painel influenciem significativamente o mercado, impulsionadas pela crescente demanda por computação de alto desempenho e soluções de IA. O cenário competitivo está a mudar à medida que as fundições e os IDMs avançam nas suas capacidades de embalagem, enquanto os novos participantes da China intensificam a concorrência. Com a miniaturização tradicional de chips chegando aos seus limites físicos, a indústria está adotando progressivamente técnicas avançadas de empacotamento para melhorar o desempenho e a integração.

Drivers de mercado

Aumento na demanda por IA e data center alimenta o crescimento do mercado

A procura por data centers já aumentou devido à crescente importância dos dados no mundo de hoje. No entanto, espera-se que esta procura cresça ainda mais com o aumento daIA generativa (geração AI). A tecnologia de empilhamento de chips 3D impacta positivamente os data centers, abrindo novas oportunidades para otimização de custos.

A infraestrutura de data centers em todo o mundo está evoluindo rapidamente para suportar recursos de IA, permitindo o processamento de grandes volumes de cálculos e requisitos complexos. As regiões Ásia-Pacífico e América do Norte lideram atualmente na proliferação de data centers, com centros importantes em cidades como Pequim, Xangai, norte da Virgínia e área da Baía de São Francisco. De acordo com um relatório de 2024 do IBM Institute for Business Value (IBM IBV), 43% dos executivos de tecnologia de nível C expressaram preocupações crescentes sobre a sua infraestrutura tecnológica nos últimos seis meses devido ao aumento da IA generativa, permitindo-lhes concentrar-se na otimização da sua infraestrutura para satisfazer as suas necessidades de escalabilidade.

Investimentos notáveis de grandes empresas de tecnologia também indicam um forte crescimento para o setor de data centers de IA. Em 2025, a Microsoft pretende investir cerca de 80 mil milhões de dólares na construção de data centers, enquanto a Meta dedica 10 mil milhões de dólares a uma nova hiperescala de quatro milhões de pés quadrados.centro de dadosprojeto na Luisiana.

Desafios de mercado

Complexidades de fabricação e aumento de custos dificultam o avanço do mercado de empilhamento 3D

Um dos principais desafios na implementação do empilhamento de chips 3D é o aumento da complexidade de fabricação. O processo exige técnicas avançadas de fabricação e equipamentos altamente especializados, o que pode elevar significativamente os custos de produção. Além disso, esta complexidade pode resultar em problemas de rendimento, impactando ainda mais a competência e a eficácia da produção.

Além disso, os materiais essenciais para a pilha 3D - como interposers de silício, vias de silício (TSVs) e micro-saliências de passo fino - contribuem para custos de produção elevados. Esses componentes exigem processos de fabricação sofisticados, aumentando os gastos com materiais e processos. Garantir a compatibilidade com arquiteturas de hardware, interfaces de software e sistemas de gerenciamento térmico existentes geralmente exige investimentos significativos e modificações no nível do sistema. Como resultado, estes desafios podem retardar a adoção mais ampla de tecnologias de pilha 3D.

Descarregue amostra grátis para saber mais sobre este relatório.

Oportunidades de mercado

Iniciativas e investimentos governamentais ativos para atender a novos caminhos de crescimento

Programas governamentais, incluindo o CHIPS e o Science Act dos EUA, estão facilitando investimentos significativos na fabricação de semicondutores. Estas iniciativas visam melhorar as capacidades de produção interna e reduzir a dependência de cadeias de abastecimento estrangeiras, criando oportunidades de crescimentoembalagem avançadatecnologias, incluindo empilhamento 3D. Por exemplo,

- Em junho de 2025,anunciou um investimento histórico de aproximadamente US$ 200 bilhões em manufatura e P&D nos EUA, ressaltando os esforços dos EUA para recuperar a liderança na indústria global de semicondutores. Esta expansão é significativamente apoiada pelo governo dos EUA, prevendo-se que a Micron receba cerca de 6,5 mil milhões de dólares em apoio ao abrigo do CHIPS e da Lei da Ciência.

Além disso, investimentos significativos por parte dos líderes da indústria - como a instalação de embalagem de chips de 2,9 mil milhões de dólares da TSMC e a expansão de 110 milhões de dólares da Fujifilm em capacidades de polimento de chips - destacam o compromisso contínuo de Taiwan em promover a excelência em semicondutores.

ANÁLISE DE SEGMENTAÇÃO

Por método

Empilhamento 3D Die-to-Wafer para solução de chip personalizado impulsiona o crescimento segmental

Com base no método, o mercado é segmentado em die-to-die, die-to-wafer, wafer-to-wafer, chip-to-chip e chip-to-wafer.

Espera-se que o método die-to-wafer ganhe a maior participação de mercado, respondendo por 28,08% em 2026. devido à sua capacidade de atender às demandas por embalagens de semicondutores de alto desempenho, econômicas e confiáveis. O método D2W permite integrar diferentes tipos de matrizes (por exemplo, lógica, memória,sensores) em um único pacote. Isto é significativo para aplicações em evolução que necessitam de soluções de chips personalizadas, como IA, 5G e IoT, aumentando assim o mercado potencial para tecnologias de pilha 3D. Por exemplo,

- Em maio de 2025,A SUSS, fornecedora global de equipamentos de semicondutores e soluções de processo, lançou a plataforma XBC300 Gen2 D2W – uma solução de ligação avançada que melhora seu portfólio de ligação híbrida. Esta nova plataforma suporta ligação de matriz a wafer (D2W) em substratos de 200 mm e 300 mm, atendendo a requisitos rigorosos de espaçamento entre matrizes e permitindo integração de alta precisão para dispositivos semicondutores de próxima geração.

No entanto, projeta-se que o método wafer-to-wafer testemunhe o maior CAGR durante o período de previsão. As conexões wafer-to-wafer apresentam rápido crescimento por meio de seus pontos de interconexão em miniatura e ofertas de fabricação de alto rendimento, o que os torna ideais para incorporação de memória, aplicações de processamento neuromórfico e tecnologias de sensores de imagem.

Por tecnologia

A crescente adoção de TSV 3D para soluções avançadas de embalagem catalisa o crescimento segmental

Com base na tecnologia, o mercado é segmentado em TSV 3D (através do Silicon Via), ligação híbrida 3D, integração 3D monolítica, entre outros.

Em 2026, espera-se que a tecnologia 3D TSV (Through-Silicon Via) detenha a maior participação de mercado, respondendo por 33,92%. destacando seu papel crítico no apoio à integração vertical em dispositivos semicondutores. Os TSVs funcionam como conexões elétricas verticais, facilitando a criação de pacotes 3D inovadores e circuitos integrados, ligando diretamente matrizes semicondutoras empilhadas. Essa tática elimina a necessidade de fiação convencional nas bordas ou wirebonding, que antigamente era usada em embalagens empilhadas em substratos orgânicos. Devido ao seu desempenho superior e capacidades de integração compactas, os TSVs são gradualmente preferidos na fabricação de produtos de última geraçãoCIs 3De arquiteturas baseadas em interposer.

Espera-se que a ligação híbrida 3D registre o maior CAGR durante o período de previsão, impulsionado pelo aumento dos investimentos em tecnologias avançadas de empilhamento de chips. Este método de ligação conecta interfaces metal-metal e dielétrico-dielétrico, reduzindo consideravelmente a resistência de interconexão e melhorando a integridade do sinal. Como resultado, ele oferece eficiência energética, desempenho e escalabilidade superiores – requisitos essenciais para aceleradores de IA, processadores de computação de alto desempenho (HPC) e soluções de memória de alta velocidade.

Por dispositivo

Aumento da demanda por memória de alta largura de banda (HBM) para impulsionar a expansão do segmento de dispositivos de memória

Por dispositivo, o mercado é dividido em MEMS/sensores, imagem e optoeletrônica, ICs lógicos, dispositivos de memória, LEDs, entre outros.

Espera-se que os dispositivos de memória sejam fundamentais na condução do mercado de empilhamento 3D, respondendo por uma participação de 27,37% em 2026. alimentados pela crescente demanda por maior desempenho, maior densidade e formatos compactos. O aumento de aplicações com uso intensivo de dados — como inteligência artificial (IA), computação em nuvem e computação de alto desempenho (HPC) — acelerou a adoção de soluções de memória empilhadas em 3D, incluindo NAND 3D, memória de alta largura de banda (HBM) e DRAM avançada. Em resposta à crescente necessidade de memória rápida e de baixa latência, os principais players, incluindo Samsung, Micron e SK Hynix, estão investindo consideravelmente em empilhamento 3D NAND e em tecnologias HBM baseadas em TSV para aumentar a densidade da memória e, ao mesmo tempo, aumentar a eficiência energética.

Espera-se que os ICs lógicos registrem o maior CAGR entre 2025 e 2032. As crescentes cargas de trabalho de computação heterogêneas,aprendizado de máquina (ML)complexidade e inteligência artificial (IA) estão impulsionando a demanda por ICs lógicos empilhados 3D, especificamente para FPGAs, aceleradores de IA e processadores. Por exemplo,

- Em agosto de 2024,A Powerchip Semiconductor Manufacturing Company (PSMC) apresentou seus interposers 2.5D com tecnologia de empilhamento de wafer multicamadas Logic-DRAM, para atender às crescentes demandas de aplicações de IA. De acordo com a empresa, os principais players – incluindo a AMD – planejam aproveitar essa tecnologia com nós lógicos avançados das principais fundições para desenvolver chips de IA 3D de alta capacidade, baixo consumo de energia e alta largura de banda.

Por indústria

Para saber como nosso relatório pode ajudar a otimizar seu negócio, Fale com um analista

Aumento da infraestrutura de rede 5G e necessidade de soluções de baixa latência para impulsionar a adoção do empilhamento 3D em TI e Telecom

Por setor, o mercado é segmentado em TI etelecomunicações, eletrônicos de consumo, automotivo, manufatura, saúde e outros.

Prevê-se que o setor de TI e telecomunicações cresça com um CAGR mais elevado durante o período de previsão, impulsionado pelo rápido crescimento no consumo de dados, pelo aumento do 5G e pela tecnologia relacionada, e pela crescente necessidade de soluções de semicondutores de alto desempenho, compactas e energeticamente eficientes. A implantação de redes 5G é um dos principais impulsionadores da crescente adoção da tecnologia 3D stack no setor de telecomunicações. Como o 5G exige velocidades de dados mais altas, baixa latência e comunicação mais eficiente entre os nós da rede, os semicondutores empilhados 3D oferecem as melhorias de desempenho necessárias.

- Em junho de 2025,A Soitec, fornecedora de materiais semicondutores, anunciou uma parceria estratégica com a Powerchip Semiconductor Manufacturing Company (PSMC). Sob esta colaboração, a Soitec concorda em fornecer à PSMC substratos de 300 mm com uma camada de liberação e prontidão para transferência de camada de transistor (TLT). Isso apoiará o empilhamento avançado de chips 3D no nível do wafer, mostrando o potencial das tecnologias de semicondutores da próxima geração.

Oindústria de eletrônicos de consumodetinha a maior participação de mercado em 2024, impulsionada pela crescente adoção de tablets de alto desempenho, wearables inteligentes e smartphones integrados com recursos de AR/VR. Esses dispositivos exigem processamento de alta velocidade e eficiência energética e soluções compactas de memória empilhada 3D para o consumidor, como 3D NAND e HBM, juntamente com ICs lógicos avançados, para aumentar a vida útil da bateria e completar o desempenho do dispositivo.

PERSPECTIVAS REGIONAIS DO MERCADO DE EMPILHAMENTO 3D

Geograficamente, o mercado é estudado na Ásia-Pacífico, América do Norte, América do Sul, Europa e Oriente Médio e África.

Ásia-Pacífico

Asia Pacific 3D Stacking Market Size, 2025 (USD Billion)

Para obter mais informações sobre a análise regional deste mercado, Descarregue amostra grátis

Ásia-Pacífico dominou o mercado com uma avaliação de US$ 0,69 bilhão em 2025 e deve atingir US$ 0,82 bilhão em 2026. A Ásia-Pacífico detinha a maior parte do mercado de empilhamento 3D em 2024, impulsionada pelas vantagens competitivas da região. Estas incluem a disponibilidade de mão-de-obra de baixo custo na China, inovações contínuas por parte das fábricas em Taiwan, fortes capacidades de produção das empresas japonesas e o estabelecimento de novas fábricas de semicondutores na China, Taiwan, Japão e Coreia do Sul. O mercado do Japão deverá atingir 0,19 mil milhões de dólares até 2026, o mercado da China deverá atingir 0,23 mil milhões de dólares até 2026 e o mercado da Índia deverá atingir 0,11 mil milhões de dólares até 2026.

O apoio governamental está acelerando ainda mais o crescimento do mercado na Ásia-Pacífico. O investimento de 11,6 mil milhões de dólares do Japão no desenvolvimento de tecnologia de semicondutores em 2023, com 30% alocados para embalagens avançadas e empilhamento 3D, está a impulsionar consideravelmente a expansão da indústria. Da mesma forma, o compromisso da Coreia do Sul de 427 mil milhões de dólares em investimentos em semicondutores até 2030 (Ministério do Comércio, Indústria e Energia) está a fortalecer o ecossistema de semicondutores da região.

O mercado chinês detinha a maior participação de mercado na região Ásia-Pacífico em 2024. O crescimento do mercado é impulsionado principalmente pela rápida expansão da fabricação doméstica de semicondutores, apoiada por iniciativas governamentais, incluindo o plano "Made in China 2025" da China. Além disso, a liderança do país em aplicações de IA e IoT, que dependem fortemente da integração heterogénea e da memória de alta largura de banda (HBM), está a alimentar a procura. O aumento da necessidade deChipsets 5G, processadores de IA e eletrônicos para veículos autônomos aceleram ainda mais a adoção da integração 3D avançada em nível de wafer, subsidiando o crescimento do mercado.

América do Norte

Em 2025, a América do Norte gerou 0,53 mil milhões de dólares, contribuindo com 25,30% para a receita do mercado global, e prevê-se que cresça para 0,65 mil milhões de dólares em 2026. Espera-se que a América do Norte experimente o crescimento mais rápido na indústria de empilhamento 3D, impulsionado pela rápida adoção de tecnologias avançadas na região e por uma elevada procura de dispositivos eficientes e compactos em vários setores. Os principais intervenientes no mercado, apoiados por investimentos substanciais em investigação e desenvolvimento, estão a impulsionar a inovação. À medida que as embalagens avançadas ganham destaque, o Arizona emerge como um centro crítico para o processo vital de fabricação. Consequentemente, os governos locais e as empresas do sector privado estão a colaborar para reforçar a posição do Arizona como líder na produção de semicondutores. O mercado dos EUA deverá atingir US$ 0,47 bilhão até 2026. Por exemplo,

- Em fevereiro de 2024,A Amkor anunciou a aprovação de sua instalação terceirizada de montagem e teste de semicondutores (OSAT) em Peoria, Arizona. Com um investimento de 2 mil milhões de dólares, a instalação pretende estabelecer um centro de embalagem robusto no Arizona e, ao mesmo tempo, criar 2.000 novos empregos para a força de trabalho local, reforçando ainda mais as capacidades de produção de semicondutores da região.

Os EUA são essenciais no mercado de empilhamento 3D, impulsionado por empresas de tecnologia influentes e forte apoio governamental. Por exemplo, a Lei CHIPS, aprovada em julho de 2022, alocou 52,7 mil milhões de dólares para iniciativas de semicondutores do ano fiscal de 2022 ao ano fiscal de 2027, dedicadas à produção e à investigação e desenvolvimento. Esses fundos apoiam o avanço de tecnologias de pilha 3D essenciais para aplicações de IA e aprendizado de máquina, solidificando ainda mais os EUA como líder na revolução de semicondutores e no design de chips de próxima geração.

Ámérica do Sul

O mercado sul-americano provavelmente registrará um CAGR modesto durante o período de previsão. O governo local tem executado políticas para atrair investimentos em tecnologia e fabricação de semicondutores, melhorando a infraestrutura e oferecendo incentivos para P&D no setor de semicondutores. Empresas como Rohm Semiconductor e Hitachi High Technologies estão estabelecendo presença no Brasil, contribuindo para o desenvolvimento de capacidades avançadas de embalagem, incluindo empilhamento 3D. A América Latina foi responsável por 0,18 mil milhões de dólares em 2025, representando 8,80% da quota de mercado global, e prevê-se que atinja 0,21 mil milhões de dólares em 2026.

Europa

O mercado europeu representou 0,42 mil milhões de dólares em 2025, representando 20,40% da indústria global, e deverá atingir 0,52 mil milhões de dólares em 2026. A Europa está preparada para capturar uma quota de mercado significativa durante o período de previsão, impulsionada pela crescente digitalização da região em todas as indústrias e pela crescente procura de dispositivos electrónicos. Para satisfazer a necessidade crescente de electrónica avançada, as empresas investem em tecnologias de ponta e expandem as suas capacidades de produção, colocando a Europa como um actor-chave no mercado. O mercado do Reino Unido deverá atingir 0,10 mil milhões de dólares até 2026, enquanto o mercado alemão deverá atingir 0,11 mil milhões de dólares até 2026.

A robusta indústria automotiva da Alemanha, impulsionada pelo desenvolvimento de veículos elétricos (EVs), condução autônoma esistemas avançados de assistência ao motorista (ADAS), está alimentando a demanda por semicondutores de alto desempenho e eficiência energética. Esses requisitos apoiam o crescimento da pilha 3D, o que aumenta a densidade do transistor e acelera o processamento de dados. Além disso, o rápido avanço da Indústria 4.0, apoiado pela liderança da Alemanha na tecnologia de computação de ponta, está a impulsionar o aumento da implementação de chips empilhados em 3D em sistemas industriais de IoT.

Oriente Médio e África

O mercado do Médio Oriente e África gerou 0,26 mil milhões de dólares em 2025, representando 12,40% do cenário do mercado global, e deverá atingir 0,3 mil milhões de dólares em 2026. O Médio Oriente e África, particularmente os EAU e a Arábia Saudita, estão a passar por um CAGR moderado impulsionado pela crescente digitalização e iniciativas governamentais. Como parte da sua iniciativa Visão 2030, a Arábia Saudita está a fazer investimentos notáveis para estabelecer capacidades locais de produção de semicondutores, abordando a cadeia de abastecimento concentrada da região. Enquanto isso, o investimento dos EAU em cidade inteligenteA infraestrutura está alimentando a demanda por soluções avançadas de semicondutores, incluindo tecnologias de pilha 3D, para dar suporte a dispositivos IoT e sistemas de computação de alto desempenho.

CENÁRIO COMPETITIVO

Principais participantes da indústria

Participantes do mercado realizam investimentos ativos em P&D e atividades de colaboração para obter vantagem competitiva

Os principais players do mercado se envolvem ativamente em P&D para inovar e avançar nas tecnologias de empilhamento 3D, com foco em melhorar o desempenho, reduzir custos e enfrentar os desafios de fabricação. Essas empresas também firmam parcerias estratégicas com líderes do setor e instituições de pesquisa para aproveitar a experiência e acelerar a adoção de soluções de pilha 3D.

- Em fevereiro de 2024,A Samsung acelerou as suas capacidades de embalagem 3D ao lançar uma linha de produção de colagem híbrida no seu centro de embalagens avançadas na Coreia. A empresa fez parceria com a Applied Materials e a Besi Semiconductor para instalar equipamentos de ligação híbrida em seu Campus Cheonan, um local crítico para a produção avançada de embalagens.

Longa lista de empresas estudadas (incluindo, mas não se limitando a)

- Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwan)

- Intel Corporation (EUA)

- Samsung Electronics Co., Ltd. (Coreia do Sul)

- Avançado Micro Dispositivos Inc.(NÓS.)

- Advanced Semiconductor Engineering Inc.

- (EUA)

- (EUA)

- Tektronix Inc.(NÓS.)

- (EUA)

- Cadence Design Systems, Inc.

- Corporação IBM (EUA)

- (EUA)

- Matéria Leve (EUA)

- Corporação Kioxia (Japão)

- Grupo JCET (China)

- Gráfico(REINO UNIDO.)

….e mais

PRINCIPAIS DESENVOLVIMENTOS DA INDÚSTRIA

- Junho de 2025:expandiu sua colaboração com a Samsung Foundry por meio de um acordo IP plurianual, estendendo as soluções de memória e interface IP da Cadence através dos nós de processos avançados SF5A, SF2P e SF4X da Samsung Foundry. Esta parceria aprimora o planejamento e a implementação de múltiplas matrizes, oferecendo fluxos de referência e kits de design de embalagens, construídos na plataforma Cadence Integrity 3D-IC, que integra embalagens, análise em nível de sistema e planejamento de sistema.

- Junho de 2025:Soitec, uma empresa francesa de materiais semicondutores, anunciou uma colaboração com a Powerchip Semiconductor Manufacturing Corporation (PSMC). Como parte do acordo, a Soitec fornecerá à PSMC substratos de 300 mm com uma camada de liberação e prontidão para transferência de camada de transistor (TLT), apoiando uma nova demonstração de empilhamento avançado de chips 3D no nível de wafer.

- Abril de 2025:A Intel revelou seu nó 14A (1,4 nm) de próxima geração como parte de seu roteiro de hardware atualizado. A empresa também apresentou seus nós 18A-P e 18A-PT. O nó 18A-P é uma variante de alto desempenho do 18A, enquanto o 18A-PT suporta Through Silicon Vias (TSVs) para empilhamento de chips 3D. Os nós da série T da Intel também integram a tecnologia Foveros Direct 3D, que compartilha características semelhantes às da tecnologia de empilhamento de chips 3D da TSMC.

- Janeiro de 2025:A Samsung Foundry fez parceria com a Dreambig Semiconductor para desenvolver a plataforma de etiqueta de chip MARS, apresentando os chips Networking IO e Chiplet Hub. Esta colaboração aproveita o empilhamento 3D avançado de chip-on-wafer da Samsung Foundry e a tecnologia de processo SF4X FinFET. Com sua ampla experiência em memória HBM e empacotamento sinérgico avançado, a Samsung Foundry trabalha em estreita colaboração com a Dreambig Semiconductor para aprimorar os recursos da plataforma.

- Novembro de 2024:Lightmatter, uma empresa de supercomputação fotônica, anunciou uma colaboração estratégica com a Advanced Semiconductor Engineering, Inc. Esta parceria visa avançar a plataforma Passage da Lightmatter, um mecanismo fotônico empilhado em 3D com fibra conectável, para resolver os gargalos críticos de interconexão de IA que atualmente limitam o desempenho da infraestrutura do data center.

- Agosto de 2024:A TSMC apresentou sua família de tecnologias 3DFabric, incluindo soluções de interconexão frontend e backend 2D e 3D. As tecnologias de front-end TSMC-SoIC (System on Integrated Chips) implementam a precisão e as metodologias das fábricas de silício de ponta, essenciais para o empilhamento de silício 3D. O processo de empilhamento de matrizes incorpora tecnologias Wafer-on-Wafer (WoW) e Chip-on-Wafer (CoW), permitindo o empilhamento 3D de matrizes idênticas e heterogêneas.

ANÁLISE DE INVESTIMENTO E OPORTUNIDADES

A indústria de empilhamento 3D está preparada para um crescimento substancial, impulsionada por avanços tecnológicos, investimentos estratégicos e políticas governamentais de apoio. Ao concentrar-se em soluções avançadas de embalagens, iniciativas de I&D e parcerias estratégicas, as partes interessadas podem capitalizar as oportunidades emergentes neste setor dinâmico. Por exemplo,

- Em junho de 2025,A GlobalFoundries, juntamente com a administração Trump e empresas líderes de tecnologia como SpaceX, Apple, Qualcomm Technologies, Inc., AMD, GM e NXP, com o objetivo de onshore componentes críticos da sua cadeia de abastecimento, anunciaram planos para investir 16 mil milhões de dólares para desenvolver as suas capacidades avançadas de embalagem e fabrico de semicondutores nas suas instalações em Vermont e Nova Iorque.

COBERTURA DO RELATÓRIO

O relatório fornece uma análise detalhada do mercado e concentra-se em aspectos-chave, como empresas líderes, tipos de produtos/serviços e principais aplicações do produto. Além disso, o relatório oferece insights sobre as tendências do mercado e destaca os principais desenvolvimentos do setor. Além dos fatores acima, o relatório abrange diversos fatores que contribuíram para o crescimento do mercado nos últimos anos.

Pedido de Personalização Para obter informações abrangentes sobre o mercado.

ESCOPO E SEGMENTAÇÃO DO RELATÓRIO

|

ATRIBUTO |

DETALHES |

|

Período de estudo |

2021-2034 |

|

Ano base |

2025 |

|

Ano estimado |

2026 |

|

Período de previsão |

2026-2034 |

|

Período Histórico |

2021-2024 |

|

Taxa de crescimento |

CAGR de19h70% de 2026 a 2034 |

|

Unidade |

Valor (US$ bilhões) |

|

Segmentação |

Por método

Por tecnologia

Por dispositivo

Por indústria

Por região

|

|

Empresas perfiladas no relatório |

Taiwan Semiconductor Manufacturing Company Limited (TSMC) (Taiwan), Intel Corporation (EUA), Samsung Electronics Co., Ltd. (Coreia do Sul), Advanced Micro Devices Inc. (EUA), Advanced Semiconductor Engineering Inc. (EUA), etc. |

Perguntas Frequentes

O mercado está projetado para atingir US$ 10,51 bilhões até 2034.

Em 2025, o mercado foi avaliado em US$ 2,08 bilhões.

O mercado deverá crescer a um CAGR de 19,70% durante o período de previsão.

Em termos de participação de mercado, o segmento TSV 3D lidera o mercado.

O aumento nas demandas de IA e data center alimenta o crescimento do mercado.

Taiwan Semiconductor Manufacturing Company Limited (TSMC), Intel Corporation, Samsung Electronics Co., Ltd., Advanced Micro Devices Inc., Advanced Semiconductor Engineering Inc., Cadence Design Systems, Inc., Texas Instruments Inc., são os principais players do mercado.

Espera-se que a América do Norte detenha a maior participação de mercado.

Por setor, espera-se que o setor de TI e telecomunicações cresça com um CAGR mais alto durante o período de previsão.

Entre em contacto com os nossos especialistas Fale com um especialista

Obtenha 20% de personalização gratuita

Ampliar a cobertura regional e por país, Análise de segmentos, Perfis de empresas, Benchmarking competitivo, e insights sobre o usuário final.

Relatórios relacionados

-

US +1 833 909 2966 (chamada gratuita)

-

Entre em contacto connosco